Zynq UltraScale MPSoC Base TRD 2016.3 - Design Module 2

Zynq UltraScale MPSoC Base TRD 2016.3 - Design Module 2

Design Overview

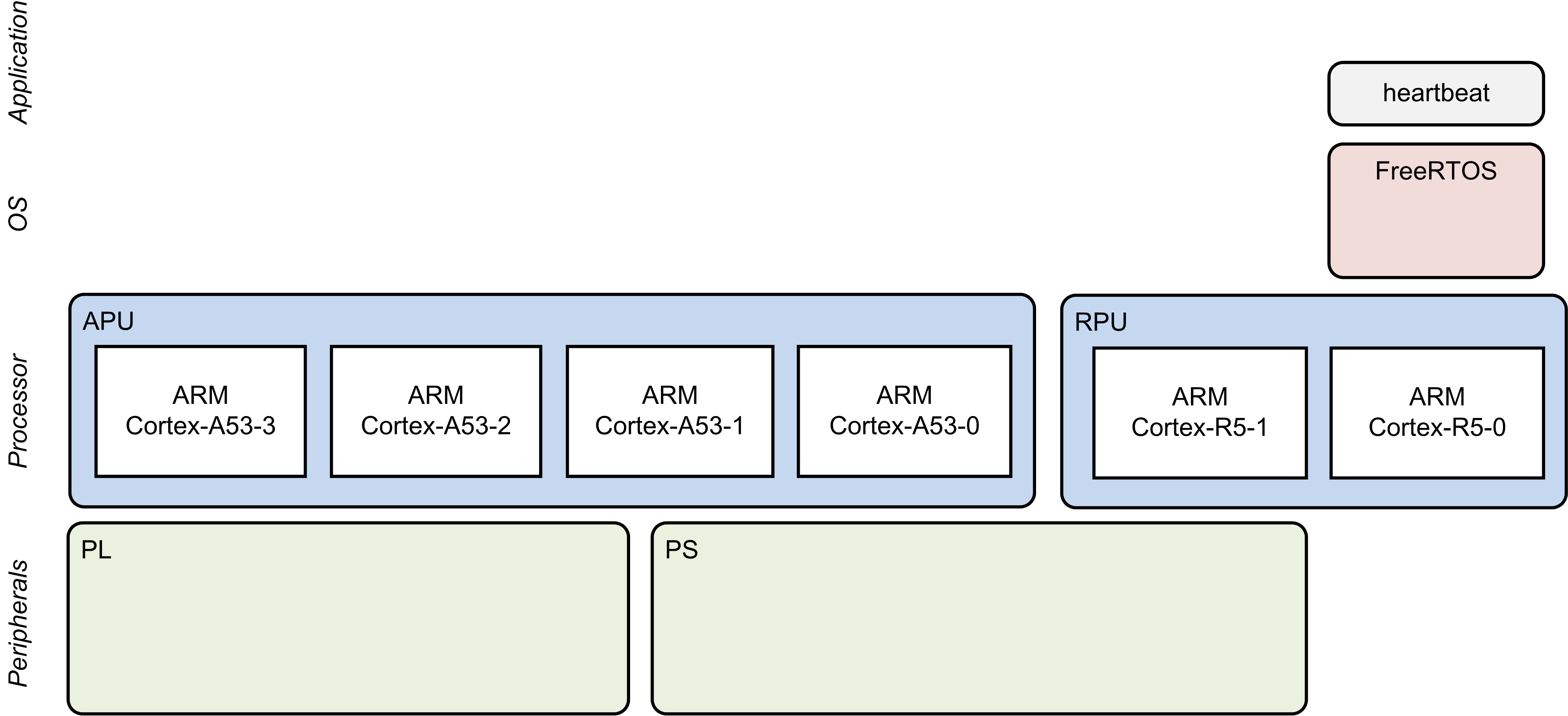

This design module demonstrates the FreeRTOS and application running on RPU-0, where:

- FreeRTOS boots on RPU-0

- FreeRTOS application "heartbeat" prints periodic messages on UART-1

Design Components

- pmu_fw

- petalinux_bsp

- zynqmp_fsbl

- heartbeat.elf

Build Flow Tutorials

PMU Firmware

Please refer to design module 1 - PMU firmware for instructions or skip this step if you have built the PMU firmware in a previous module.

Heartbeat Application

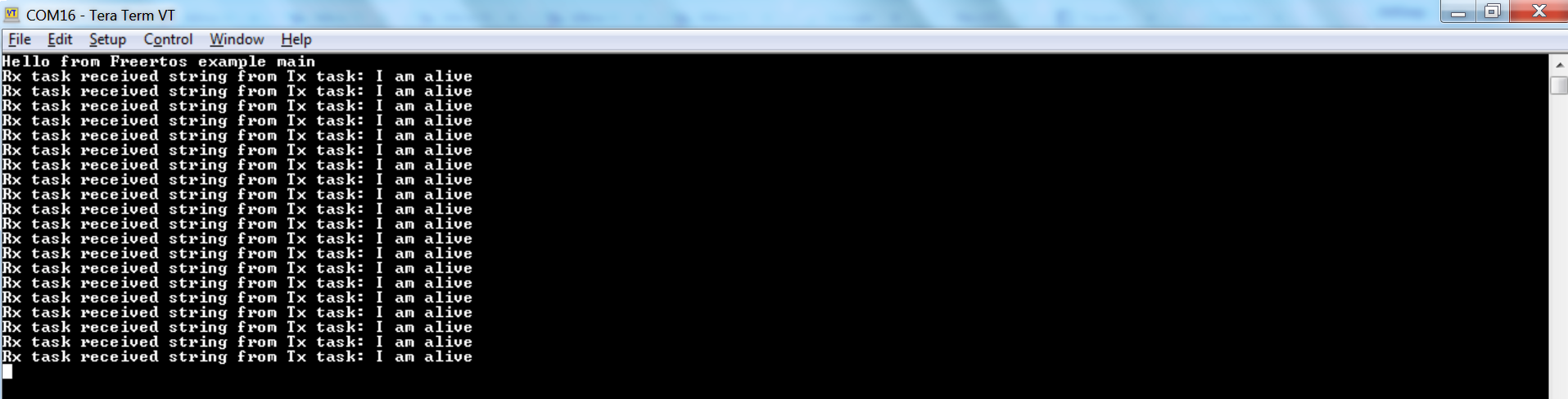

The heartbeat application is a FreeRTOS application that executes on RPU-0 after the FSBL has finished. This application is a simple dual task application that demonstrates communication between the two tasks by printing messages to the UART1 console.

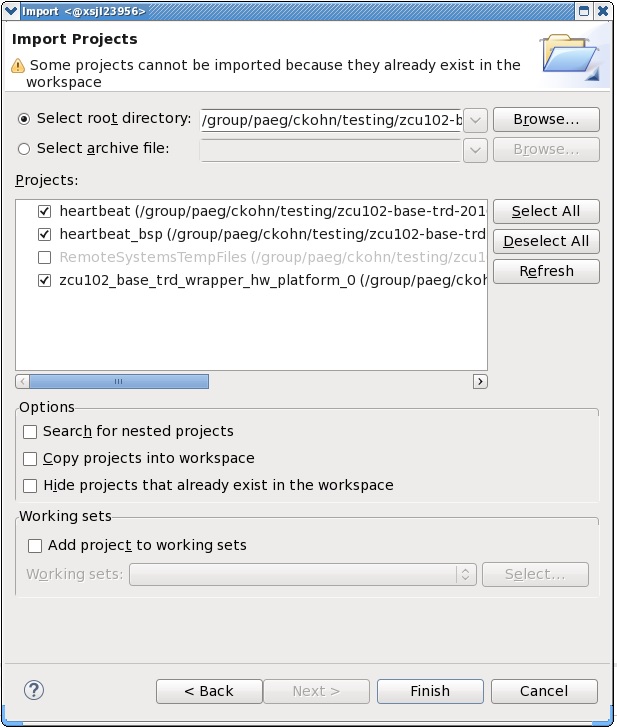

Create a new XSDK workspace.

% cd $TRD_HOME/rpu0/heartbeat % xsdk -workspace . &&

- Click 'Import Project' from the welcome screen, browse to the current working directory and make sure the heartbeat, heartbeat_bsp, and zcu102_base_trd_wrapper_hw_platform_0 projects are selected. Click Finish.

- Right-click on the heartbeat project and select 'Build Project'.

Copy the generated heartbeat executable into the PetaLinux BSP.

cp heartbeat/Debug/heartbeat.elf $TRD_HOME/apu/petalinux_bsp/images/linux

PetaLinux BSP

This tutorial shows how to build the first stage bootloader (FSBL) and boot image using the PetaLinux build tool.

The petalinux-config step can be skipped if this was already done in a previous module.

% cd $TRD_HOME/apu/petalinux_bsp % petalinux-config --get-hw-description=./hw-description --oldconfig

Build the FSBL. This step can be skipped if this was already done in a previous module.

petalinux-build -c bootloader

Create a boot image.

% cd images/linux % petalinux-package --boot --bif=dm2.bif --force

Copy the generated boot image to the dm2 SD card directory.

% mkdir -p $TRD_HOME/images/dm2 % cp BOOT.BIN $TRD_HOME/images/dm2

Run Flow Tutorial

- See here for board setup instructions.

- Copy all the files from the $TRD_HOME/images/dm2 SD card directory to a FAT formatted SD card.

- Power on the board to boot the images; make sure all power rail LEDs are lit green.

- The user can now see FSBL and PMU-firmware prints on UART-0 and prints from heartbeat application can be viewed on UART-1 which is shown in the following picture:

, multiple selections available,

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy