/

ZCU102 Cross Trigger Debug

ZCU102 Cross Trigger Debug

This demos has been created to test Cross Triggering Debug feature, included in the SDK 2016.3 release. Two different use cases are pres

Table of Contents

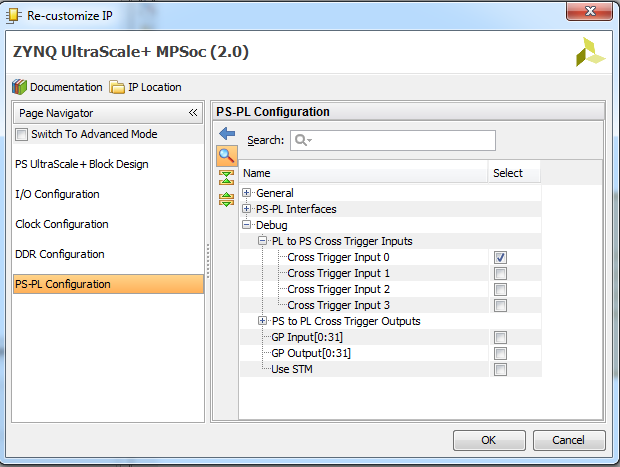

Build Hardware Platform

Note: The 1.3 version of the zcu102 board files in needed here. These can be downloaded from the headstart lounge prior to completing this demo.Include a ZYNQ MPSoC device, run default configuration wizard and enable one PL-PS cross triggering port. Also include an ILA IP and configure with the following values.

Include a dummy peripheral in the BD (ie. AXI Timer) and connect the blocks to generate a valid platform design.

Save the project, generate the bitstream and once generated export and launch the SDK.

PL-PS Cross Trigger

This demos is indeed to show how a hardware trigger event can be used to generate a software halt (processor halt) to debug both sides of the device.

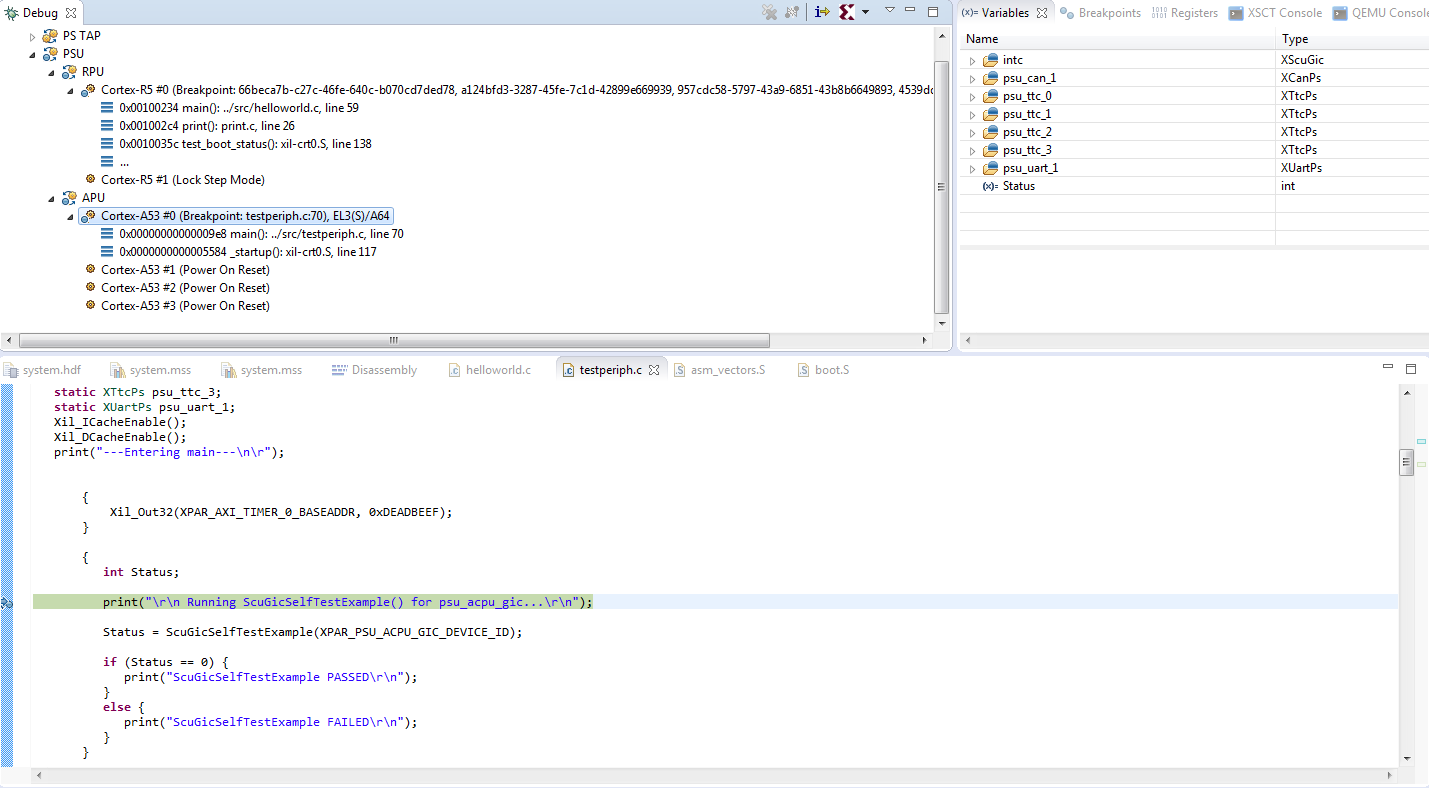

Create a peripheral test application for A53 core, and modify the main function (testperiph.c) to include a dummy bus access to the AXI Timer, which is going to be used to trigger the debugger.

Xil_Out32(XPAR_AXI_TIMER_0_BASEADDR, 0xDEADBEEF);

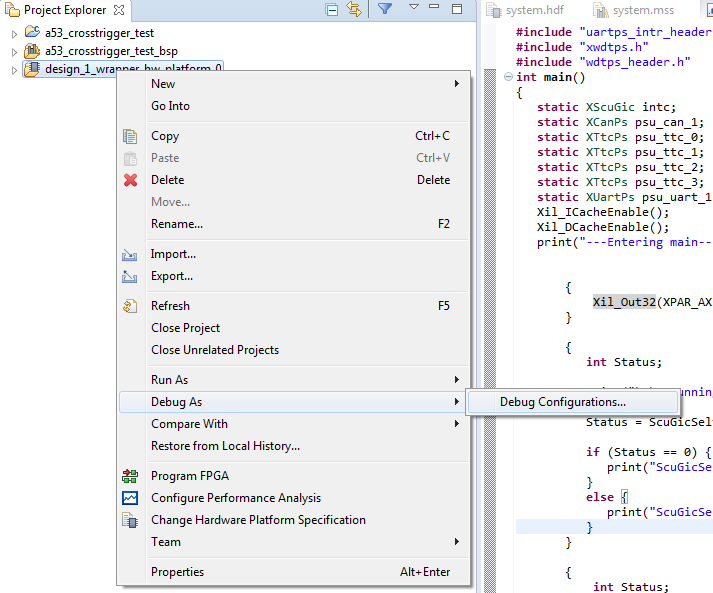

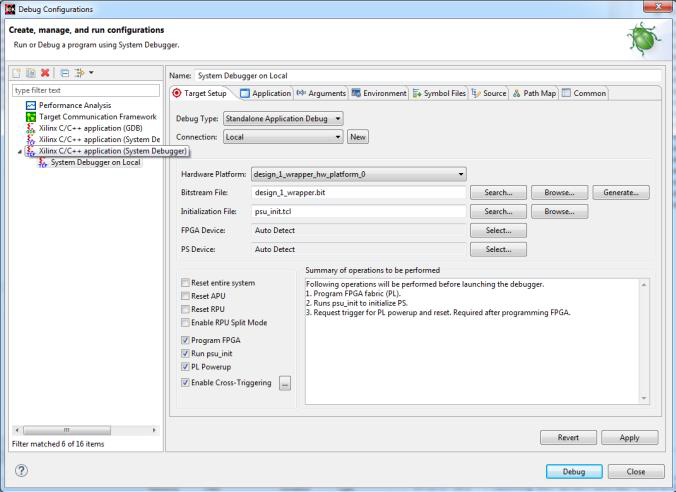

Create a new Debug Configuration

Important: There is a bug in the 2016.3 version of SDK, wherein the zynqmp device is not detected if the debug configuration is not created in the following way

Ensure that the Target Setup includes the following features

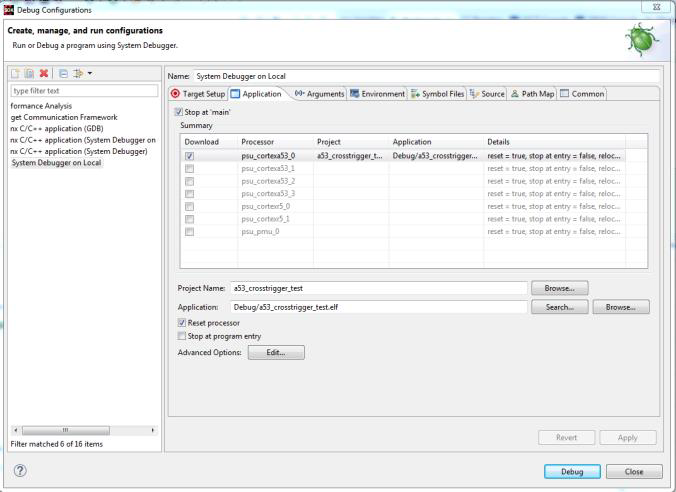

Select the application test in the Application tab and enable stop at program entry checkbox

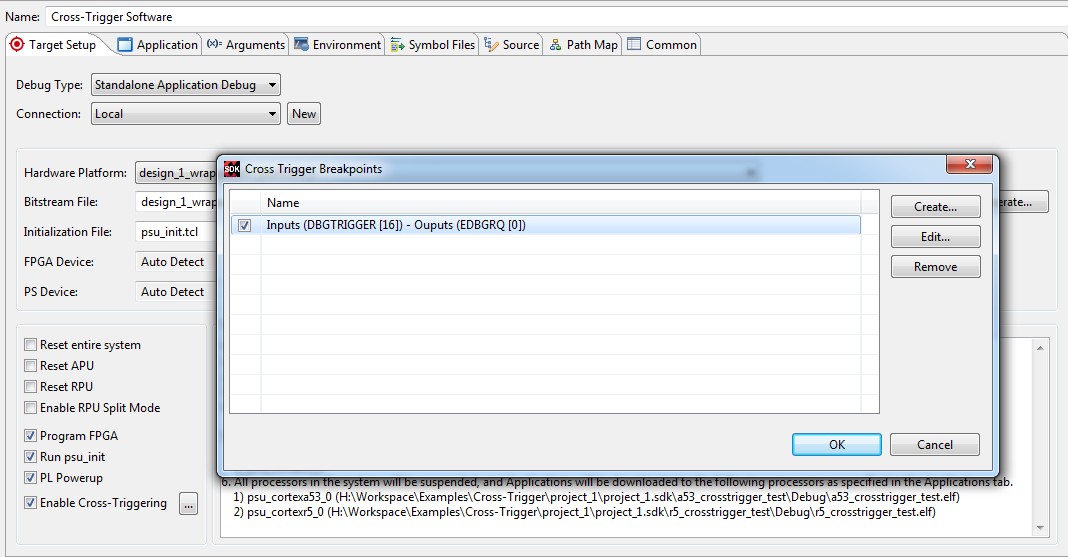

Select the advanced features of Cross-Triggering and create a new Breakpoint. In this case cross-trigger input will be any FTM register and as output A53-0 Debug register. Apply and Debug the configuration in order to check that the breakpoint tab shows the cross-trigger.

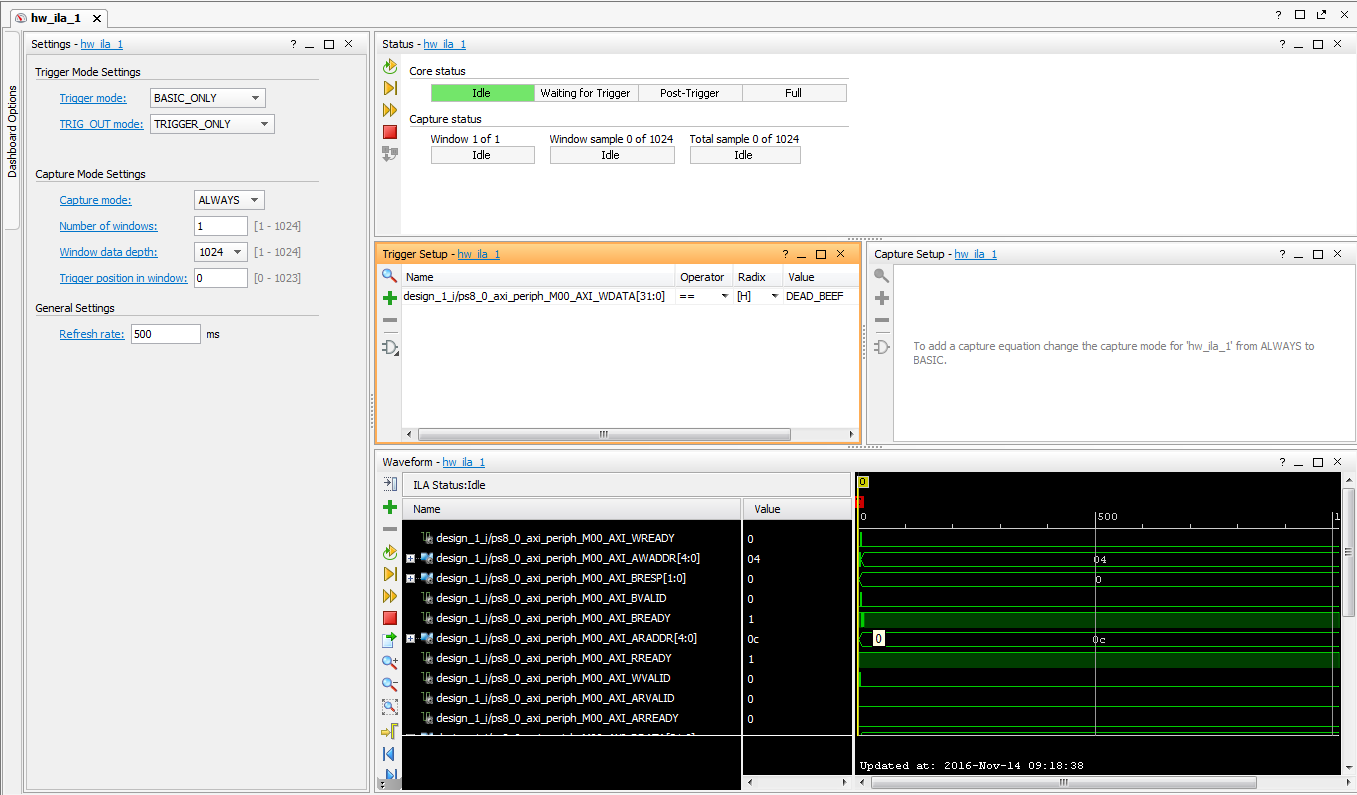

On the other hand open the hardware manager (within Vivado project) and connect to the target. Set a new trigger setup to catch the trigger condition we build in the software (WDATA = 0xDEADBEEF), and modify the TRIG_OUT mode value to generate a trigger output that will be used to halt the A53#0 processor.

Once everything is setup, run the trigger in the ILA core and run the software debugger. Once the ILA trigger condition is met in Vivado the core will be full and software debugging will be halted as expected in the cross-trigger configuration.

PS internal Cross-Trigger

The second use case demo configures a cross-trigger between A53 and R5 cores, which can be util in AMP environments.Create an R5 application with Hello World template and include an infinite loop to generate processor halts from the A53 application.

int main()

{

init_platform();

print("Hello World\n\r");

while(1);

cleanup_platform();

return 0;

}

Generate a new Debug configuration (using hardware platform project) with the following crosstrigger configuration.

Important: There is a bug in the 2016.3 version of SDK, where in the zynqmp device is not detected if the debug configuration is not created in the following way

Add both applications to the applications tab

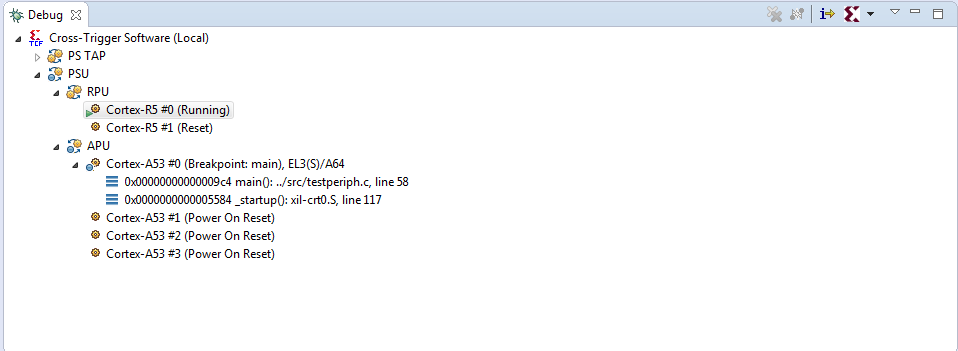

Apply and debug the application. Once started select the R5#0 core and make in run in the infinite loop while A53#0 is in the startup breakpoint.

Change to the A53#0 core, define a breakpoint and run the application. Once breakpoint is achieved a cross-trigger will be generated to stop the R5#0 core.

, multiple selections available,

Related content

Testing UIO with Interrupt on Zynq Ultrascale

Testing UIO with Interrupt on Zynq Ultrascale

More like this

ZynqMP DDRless System

ZynqMP DDRless System

More like this

Zynq UltraScale Plus MPSoC - PL Temperature and Voltage Monitor

Zynq UltraScale Plus MPSoC - PL Temperature and Voltage Monitor

More like this

Zynq Linux

Zynq Linux

Read with this

Using the JTAG to AXI to test Peripherals in Zynq Ultrascale

Using the JTAG to AXI to test Peripherals in Zynq Ultrascale

More like this

How to debug Linux Application in SDK 2019.1

How to debug Linux Application in SDK 2019.1

More like this

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy