/

ZU+ Example - Power Off Suspend

ZU+ Example - Power Off Suspend

Table of Contents

Prerequisites

- You have a ZCU102 development board.

- You have a linux machine to build images.

- You have used the Petalinux (2018.1 or later) to build.

- You have familiar with Vivado (2018.1 or later release)

Introduction

Power off suspend is the new feature in the Xilinx Power Management where APU, RPU and PMU will be power down and current state will be stored on DDR Memory.Except clock all other peripherals such as UART,OCM,TCM will be powered down. MSP430 processor will be used as source for waking up the system.

Power Off Suspend has been implemented for the ZCU102 board only (testing was done on a single board at room temperature, so PVT testing was not performed).

Steps for Enabling Power off Suspend feature

Create HDF with GPO2 polarity to High

Source petalinux settings.

source <plnx-settings.sh>

Create petalinux project using below command.

petalinux-create -t project -s <petalinux BSP path>

- Start Xilinx Vivado 2018.1

- Open existing petalinux project from Vivado. (Located at <plnx-proj-root-dir>/hardware/xilinx-zcu102-2018.1/xilinx-zcu102-2018.1.xpr)

- Open block design, customize block design using double click on "Zynq UltraScale+ MPSoC" block. (or right click and then click on "Customize Block" option)

- On the "Page Navigator" bar, click on I/O configuration.

- Go to Low Speed -> IO Peripherals -> PMU -> GPO2. Default polarity of GPO2 is low. Change GPO2 polarity to high as per below snapshot and click "OK".

- In the Flow Navigator → PROGRAM and DEBUG, click on "Generate Bitstream" option.

- Export HDF file

- Go to File → Export → Export Hardware

- Check "Include bitstream in HDF" option. Set export path if required or keep it default(<Local to Project>). Click "OK"

- In case of default path, HDF file will be generated at <workspace>/<project_name>/<project_name>.sdk/<block_name>.hdf.

Build images using Petalinux

Source petalinux settings:

source <plnx-settings.sh>

Create petalinux project using below command:

petalinux-create -t project -s <petalinux BSP path>

Configure petalinux using custom HDF (generated in previuos steps) using below command:

petalinux-config --get-hw-description=<HDF file root directory path> --oldconfig

- Enable ZynqMP firmware debugfs config in Linux kernel (ZYNQMP_FIRMWARE_DEBUG) using below steps:

- Run "petalinux-config -c kernel" command.

- Go to Firmware Drivers -> Zynq MPSoC Firmware Drivers and enable Xilinx Zynq MPSoC firmware debug APIs.

- Save configuration and exit from that.

- Enable POS related build flag in FSBL (ENABLE_POS) using below steps:

- Create project-spec/meta-user/recipes-bsp/fsbl/fsbl_%.bbappend file if not present.

Append below line in that file.

YAML_COMPILER_FLAGS_append = " -DENABLE_POS"

- Enable POS related build flag in PMUFW (ENABLE_POS) using below steps:

- Create project-spec/meta-user/recipes-bsp/pmu/pmu-firmware_%.bbappend file if not present.

Append below line in that file.

YAML_COMPILER_FLAGS_append = " -DENABLE_POS"

Build petalinux using below command:

petalinux-build

Run below command inside petalinux root directory to generate BOOT.BIN:

petalinux-package --boot --fsbl images/linux/zynqmp_fsbl.elf --u-boot images/linux/u-boot.elf --pmufw images/linux/pmufw.elf --atf images/linux/bl31.elf --fpga

- Built images (BOOT.BIN and image.ub) are present at <plnx_root_dir>/images/linux/

Sample Images:

- HDF generated from petalinux 2018.2 reference project.

zcu102_wrapper.hdf - Below is the images which is generated from petalinux 2018.2 using above HDF

- ATF bl31.elf

- PMUFW pmufw.elf

- U-Boot u-boot.elf

- Bitstream system.bit

- FSBL zynqmp_fsbl.elf

- BOOT.BIN boot.bin

- image.ub image.ub

MSP430

Please click on the link to read about MSP430 procedure -Zynq UltraScale+ MPSoC Power Advantage Tool part 7 - Building and Running the MSP430 Design from Sources

For enabling power off suspend feature user needs to replace the current MSP430.txt file with the new MSP430.txt file.

Update MSP430 firmware with the image below:

Steps to do Power off Suspend

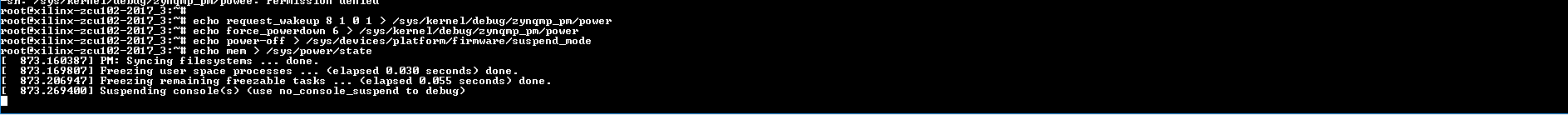

To suspend, type this in the Linux console:(For 2018.1 and 2018.2)

echo pm_request_wakeup 8 1 0 1 > /sys/kernel/debug/zynqmp-firmware/pm echo pm_force_powerdown 6 > /sys/kernel/debug/zynqmp-firmware/pm echo disabled > /sys/devices/platform/amba/ff9d0000.usb0/fe200000.dwc3/xhci-hcd.0.auto/power/wakeup echo power-off > /sys/devices/platform/zynqmp-power/suspend_mode echo mem > /sys/power/state

(For 2018.3)

echo disabled > /sys/devices/platform/amba/ff9d0000.usb0/fe200000.dwc3/xhci-hcd.0.auto/power/wakeup echo power-off > /sys/devices/platform/zynqmp-power/suspend_mode echo mem > /sys/power/state

(For 2019.1)

echo disabled > /sys/devices/platform/amba/ff9d0000.usb0/fe200000.dwc3/xhci-hcd.0.auto/power/wakeup echo power-off > /sys/devices/platform/firmware:zynqmp-firmware/firmware:zynqmp-firmware:zynqmp-power/suspend_mode echo mem > /sys/power/state

(For 2022.1 - Later)

echo disabled > /sys/devices/platform/axi/ff9d0000.usb0/fe200000.usb/xhci-hcd.1.auto/power/wakeup echo power-off > /sys/devices/platform/firmware:zynqmp-firmware/firmware:zynqmp-firmware:zynqmp-power/suspend_mode echo mem > /sys/power/state

After using above command on the linux console, system will go to power off suspend mode.

In power off suspend

LED such as DS24, DS26,DS21, PSPLL and PSAUX should be in off state.

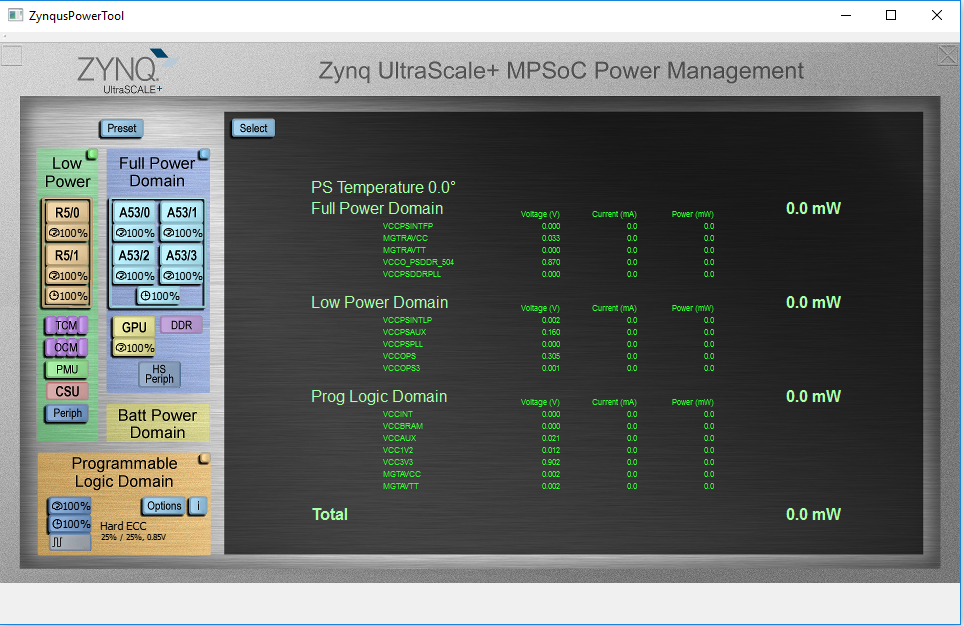

If user uses power advantage tool then user will see that power reading of FPD, LPD and PL domain should be 0 mW.

Note:- At a time user can either use power adavantage tool or MSP430 console as both uses same com port.

For resuming the linux user needs to open UART Interface 3 port.

Go to Device Manager -> Ports

See the com port number for UART Interface 3

Now go to Tera Term/PuTTY (for opening port) and open this port. Here Ex. COM9 at baud rate - 1152000.

Now to resume, type this in the MSP430 console i.e. on port COM9:

@wake

After sending @wake signal to com port system will wake up and user can see logs on the Linux console.

In power off suspend

LED such as DS24, DS26,DS21, PSPLL and PSAUX should be in off state.

If user uses power advantage tool then user will see that power reading of FPD, LPD and PL domain should be 0 mW.

Note:- At a time user can either use power adavantage tool or MSP430 console as both uses same com port.

For resuming the linux user needs to open UART Interface 3 port.

Go to Device Manager -> Ports

See the com port number for UART Interface 3

Now go to Tera Term/PuTTY (for opening port) and open this port. Here Ex. COM9 at baud rate - 1152000.

Now to resume, type this in the MSP430 console i.e. on port COM9:

@wake

After sending @wake signal to com port system will wake up and user can see logs on the Linux console.

Note: Since PL is powered down during PoS, user application needs to take care of loading the PL bitstream explicitly

after resuming from PoS if any application is using the PL resources.

Related Links

- Zynq UltraScale+ MPSoC Power Off Suspend

- Deep Sleep

- Hello World

- Power Advantage Tool

- Zynq UltraScale+ MPSoC Power Management

, multiple selections available,

Related content

Zynq UltraScale+ MPSoC Power Management - ZCU102 SW Design Examples

Zynq UltraScale+ MPSoC Power Management - ZCU102 SW Design Examples

More like this

Zynq UltraScale+ MPSoC Power Off Suspend

Zynq UltraScale+ MPSoC Power Off Suspend

More like this

Zynq UltraScale+ MPSoC Power Management

Zynq UltraScale+ MPSoC Power Management

Read with this

ZU+ Example - Deep Sleep

ZU+ Example - Deep Sleep

More like this

Zynq UltraScale+ MPSoC Restart solution

Zynq UltraScale+ MPSoC Restart solution

Read with this

Zynq UltraScale+ MPSoC Power Management - Linux Kernel

Zynq UltraScale+ MPSoC Power Management - Linux Kernel

More like this

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy