Zynq UltraScale+ MPSoC - PS Temperature and Voltage Monitor

Table of Contents

Requirements

- ZCU102 development board (This design example has been tested on silicon 4.0 rev1.0 board)

- SDK (2017.4 release and above)

Design Implementation

This design example initializes, configures and monitors PS on-chip temperature and various voltages from PMU Microblaze periodically. Following is the design implementation:- PMU Firmware application runs on PMU Microblaze. It registers a new module for monitoring PS on-chip temperature and voltages using PSU Sysmon driver APIs.

- This module initializes the System Monitor device driver instance.

- It runs the self-test on the device.

- It sets up the sequence registers to continuously monitor the following channels:

- Temperature for RPU MPCore(Temp_LPD)

- Temperature for APU MPCore (Temp_FPD)

- LPD Power Supply (VCC_PSINTLP)

- FPD Power Supply (VCC_PSINTFP)

- PS auxiliary voltage (VCC_PSAUX)

- PS I/O bank 504: DDR PHY (VCC_PSINTFP_DDR)

- PS I/O bank 503: boot config, JTAG, error, SRST, POR( VCCO_PSIO3)

- PS I/O bank 500: MIO[0:25] (VCCO_PSIO0)

- PS I/O bank 501: MIO[26:51] (VCCO_PSIO1)

- PS I/O bank 502: MIO[52:77] (VCCO_PSIO2)

- GTR SerDes I/O (PS_MGTRAVCC)

- GTR SerDes terminators (PS_MGTRAVTT).

- PS SYSMON ADC circuitry (VCCAMS).

- It enables the channel sequencer in continuous sequencer cycling mode to start the sequence.

- And it adds a scheduler task to read the latest on-chip temperature and voltages continuously for every 10 seconds and prints on the terminal.

Application creation steps

- Create FSBL application either for A53 or for R5 processor.

- Create PMU Firmware application. Download this zip file , extract and add the extracted source files to the PMU Firmware application.This creates a new custom module in PMU Firmware which initializes sysmon and monitors PS temperature and voltages periodically in continuous sequencer cycling mode. Please refer to "Custom Module Usage" section in chapter 10 in Zynq UltraScale+ MPSoC Software Developer Guide for reference.

- Enable scheduler module by defining ENABLE_SCHEDULER macro and rebuild the PMU Firmware application.

Steps to create boot image

- In SDK, go to Xilinx -> Create Boot Image. Create Boot Image window appears as below

- Select Zynq MP in Architecture category. Select Create new BIF file option.

- Browse and select path for Output BIF file path.

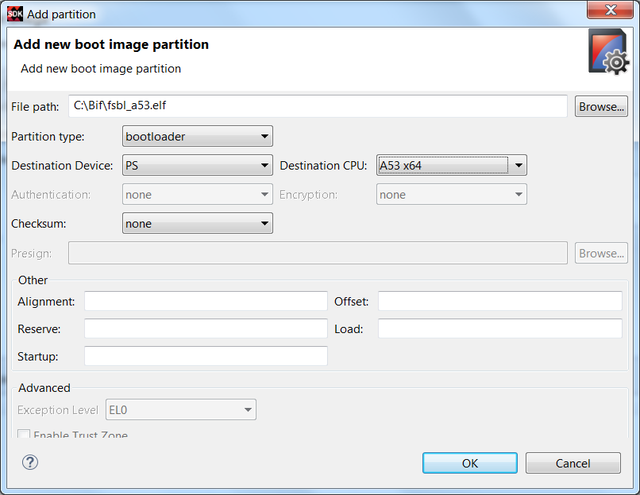

- Click on Add button to add partition. Select fsbl_a53 executable path at File path. Select Partition type as bootloader, Destination Device as PS and Destination CPU as A53 x64. Click OK.Please see the below image for reference

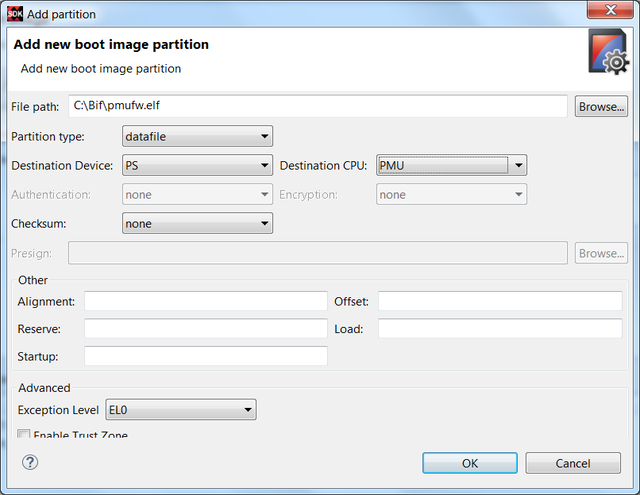

- Click on Add button to add PMU Firmware partition. Select pmu_firmware executable file path at File path. Select Partition type as datafile, Destination Device as PS and Destination CPU as PMU. Click OK. Please check below image for reference.

- .Now click on Create Image. BOOT.BIN is created at Output BIF file path. Copy the BOOT.BIN to SD card and power-on ZCU102 board in SD boot mode. And observe the prints on UART terminal.

Snippet of BIF file

Below is the snippet of BIF file created with the steps mentioned above

//arch = zynqmp; split = false; format = BIN

the ROM image:

{

[fsbl_config]a53_x64

[bootloader]C:\images\fsbl_a53.elf

[destination_cpu = pmu]C:\images\pmufw.elf}

<span style="background: white;"><span style="font-size: 10.0pt;">//arch = zynqmp; split = false; format = BIN

<span style="background: white;"><span style="font-size: 10.0pt;">the_ROM_image:

<span style="background: white;"><span style="font-size: 10.0pt;">{

<span style="background: white;"><span style="font-size: 10.0pt;"> [fsbl_config]a53_x64

<span style="background: white;"><span style="font-size: 10.0pt;"> [bootloader]C:\Images\fsbl_a53.elf

<span style="background: white;"><span style="font-size: 10.0pt;"> [destination_cpu = pmu]C:\Images\pmufw.elf

<span style="background: white;"><span style="font-size: 10.0pt;">}

<span style="background: white;">

Snippet of BIF file

Related Links

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy