Zynq-7000 Analog Data Acquistion using AXI_XADC

Table of Contents

1 Introduction

This page provides introduction and steps to build the various artifacts used in the Analog Data Acquisition application note (XAPP1183). It is demonstrated on ZC702 Evaluation kit which is based on a XC7Z020 CLG484-1 Zynq-7000 SoC device.

1.1 Detailed Description

The Zynq-7000 family is based on the Xilinx SoC architecture. These products integrate a feature-rich dual-core ARM® Cortex™-A9 based processing system and 28 nm Xilinx programmable logic (PL) in a single device. The ARM Cortex-A9 CPUs are the heart of the PS

and also include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces. XADC is an integrated 12-bit, 17 channel, 1 Ms/s ADC. The Zynq-7000 SoC PS communicates with the XADC using an AXI interface when the XADC is instantiated in the PL. XADC is an embedded block available in all Zynq-7000 SoCs.The LogiCORE™ XADC wizard IP provides an AXI4-Lite compatible interface and an optional AXI4-Stream interface. The AXI4-Lite interface is used to configure the XADC, and the AXI4-Stream interface is used for data communication. The AXI4-Stream interface includes options for interfacing the XADC data interface to other signal processing IP. This application note demonstrates using the AXI4-Lite interface to control the XADC configuration parameters, and using the AXI4-Stream interface to capture samples of the input analog data.This application note provides a hardware design in the PL that establishes the datapath between the XADC and the PS using the general-purpose (GP) port interface. An AXI DMA isused to interface to the XADC AXI4-Stream interface, and the DMA stores XADC samples in the PS DDR3. The Cortex-A9 processor is used to configure the XADC for user-specific configuration parameters. A LabView based GUI interface is provided to configure the XADC and display the collected samples.The samples are analyzed in the GUI to plot the linearity of the samples and various performance characteristics of the XADC,including signal-to-noise ratio (SNR), total harmonic distortion (THD), signal-to-noise and distortion (SINAD), and effective number of bits (ENOB). The LabView GUI interfaces to the XADC with the UART interface.

This highlights of this application note are:

- How to quickly establish an interface between Zynq-7000 PS and XADC using AXI interface

- Showcase optimized analog data acquisition using Zynq XADC.

2 Package Content

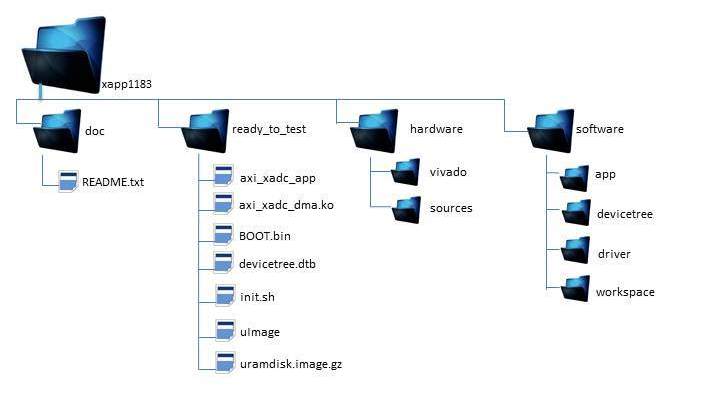

Application note package contains hardware/software sources along with ready to test binaries.

An archive with application note files can be downloaded here . (Requires signup in www.xilinx.com)

The following Figure shows the directory structure tree.

3 Prerequisites

- The ZC702 Evaluation Kit ships with the version 14.x Device-locked to the Zynq-7000 XC7Z020 CLG484-1 device and all required licenses to build the application note. For additional information, refer to UG798 ISE Design Suite 14: Installation and Licensing Guide.

- A Linux development PC with the ARM GNU tools installed. The ARM GNU tools are included with the Xilinx ISE Design Suite Embedded Edition or can be downloaded separately.

- A Linux development PC with the distributed version control system Git installed. For more information, refer to Using Git and to UG821: Xilinx Zynq-7000 EPP Software Developers Guide.

Tools for Software build

For building Linux kernel ,drivers and application:

- Xilinx XSDK 14.6/2013.2

- ARM cross compile tool

- mkimage

- corkscrew

- git

From here onward lets consider the unzipped package is available at $ZYNQ_AXI_XADC_HOME. $ZYNQ_AXI_XADC_HOME/software/workspace can be used for development area.

4 Build Hardware components

Follow the below steps to build the Hardware design

1. Browse to $ZYNQ_AXI_XADC_HOME/hardware/vivado/scripts

2. Type the below command on Linux/Windows command line:

bash> vivado -source axi_xadc_gui.tcl

The above step will open Vivado GUI and the project.

3. Click on Generate Bitstream option which generates the bitstream

4. Go to File-> Export -> Export Hardware for SDK option and click OK

5 Build software components

5.1 Standard Zynq Software Components

- Includes creation of FSBL (First Stage boot loader) . FSBL used in the application note is based on zc702_hw_platform(predefined).

- Building of FPGA Hardware bitsream using Xilinx Vivado™ Design Suite

- Building Xilinx configured uboot (Second stage boot loader) for zc702 board. Check out tag "xilinx-v14.6" and follow standard uboot build process.

- Create BOOT.bin (zynq_fsbl.elf ,system.bit and u-boot.elf)

NOTE: Building standard software/hardware components are not covered in this application note and avoided for simplicity.

User may refer to detail steps mentioned in Zynq Base TRD 14.5 wiki which are identical to this application note requirements.

5.2 Build Xilinx kernel

Steps for building the Linux kernel.Set the CROSS_COMPILE environment variable and add it to your PATH.

bash> export CROSS_COMPILE=arm-xilinx-linux-gnueabi- bash> export PATH=/path/to/cross/compiler/bin:$PATH

Linux kernel compilation internally uses mkimage command for creating uImage (Linux Kernel Image).

Hence path for mkimage command should also be added in PATH environment variable as shown below.

One can use the mkimage command that is built during u-boot building process (Section 4.1).

Clone the latest Zynq Linux kernel git repository from the Xilinx git server.

bash> cd $ZYNQ_AXI_XADC_HOME bash> git clone git://github.com/Xilinx/linux-xlnx.git

Create a new branch named zynq_axi_xadc_dma based on the xilinx-v14.6

bash> cd $ZYNQ_AXI_XADC_HOME/linux-xlnx bash> git checkout -b zynq_axi_xadc_dma xilinx-v14.6

Configure the Linux kernel for zc702 default configuration

bash> make ARCH=arm xilinx_zynq_defconfig

Build the Linux kernel. The generated kernel image can be found at $ZYNQ_AXI_XADC_HOME/linux-xlnx/arch/arm/boot/uImage.

bash> make ARCH=arm uImage modules UIMAGE_LOADADDR=0x8000

5.3 Building the Linux Device Tree Blob

Device tree configures kernel loglevel to "1". It also adds Xilinx DMA engine, AXI XADC DMA nodes to default ZC702 device-tree.

Compile the device tree source provided as part of application note package.

The output of this step is a device tree blob and can be found at $ZYNQ_AXI_XADC_HOME/linux-xlnx/devicetree.dtb.

bash> cd $ZYNQ_AXI_XADC_HOME/linux-xlnx bash> ./scripts/dtc/dtc -I dts -O dtb -o devicetree.dtb $ZYNQ_AXI_XADC_HOME/software/devicetree/zynq-zc702-xadc-dma.dts

5.4 Build LInux AXI XADC DMA Driver

This driver configures AXI XADC and DMA IP. It provides a character driver interface to the user application for reading ADC samples .It is designed based on standard Linux DMA API framework.

Linux AXI DMA driver is build a loadable module, which can be easily modified as per user requirements.

For compiling the kernel Makefile KDIR environment variable needs to point to Linux kernel source repository.User may need to modify it for linking with existing kernel sources.

bash> cd $ZYNQ_AXI_XADC_HOME/software/driver bash> make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi-

5.5 Build Linux User Application

User application communicates with kernel driver and Lab View GUI. It configures Linux driver using standard IOCTL interface,read samples and store it configured circular buffers.Read commands from Lab View GUI through UART interface and reply with appropriate response.

For building it run make command on bash terminal.

bash> cd $ZYNQ_AXI_XADC_HOME/software/app bash> make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi-

6 Setup Requirement

1. The ZC702 evaluation board with the XC7Z020 CLG484-1 part2. XAPP1183 zip file containing the design files and ready_to_test executables

2. Signal generator to test externally applied analog signal

4. Mini USB cable

5. Class 4 equivalent SD card

6. A control PC

7. AMS101 evaluator GUI.

Please follow the instructions in AMS101 targeted reference design to install the AMS101 GUI installer.

8. Terminal emulator software. i.e Teraterm

7 Execution Steps

This section summarizes the execution steps of the XAPP on ZC702 platform.

7.1 ZC702 Initial Setup

1. All jumpers and switches should be in default setting except SW16.

Mode switch SW16 should be set to boot from SD card.

Use the following switch settings:

SW16.1: OFF

SW16.2: OFF

SW16.3: ON

SW16.4: ON

SW16.5: OFF

2. Connect the AC power adapter

3. If USB-to-UART bridge is used, connect USB Mini-B side of USB-to-Mini-B cable to the on-board mini USB connector (J17). Connect USB side to the control PC.

7.2 Execution steps

1. Copy the XAPP binaries to SD card partition. XAPP1183 binaries can be found at $ZYNQ_AXI_XADC_HOME/ready_to_test directory.

2. Connect Xilinx AMS101 Evaluation Card output to ZC702 evaluation board XADC HDR slot ,and provide analog signal using external signal generator.

3. Configure SD boot mode and power on ZC702 evaluation board.

4. Initialization script provided in the package auto configures required setup. On start-up it loads the kernel module and then run the Linux user application.

5. Run AMS evaluator GUI on host PC.

6. Select appropriate COM port in LabView and click on connect TAB.

7 Setup is now configured and ready to use. Select continuous/single data acquisition mode on LabView GUI.

8 Depending on external signal input , real-time samples are captured and displayed in time/frequency domain.

NOTE: User application running on zc702 evaluation can terminated by typing "E" on teraterm console.

8 References

- User Guide for XAPP1183

- Documentation for Xilinx AMS Evaluator card.

- Documentation for Zynq-7000 SoC

- Documentation for ZC702 Evaluation Kit

- Main Xilinx wiki

Related content

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy