This tutorial explains procedure to measure transition times and respected power values when either PS or PL suspends or wake up. By following below procedure, user can see/measure the suspend/wake-up time and power. These procedures are for 2021.2 release.

Table of Contents

Different power states and measure transition time

Workloads on each domain

PLD: Petalinux prebuilt design which does not contain any specific logic

FPD: APU is running Linux script which controls PLD on/off and handshakes RPU for self suspend/off/resume

LPD: RPU is running baremetal application which controls FPD domain on/off

Prebuilt binaries for reference

For ZynqMP

Petalinux 2021.2 generated images (including other intermediate files):

Linux log:

RPU source:

For Versal

Petalinux 2021.2 generated images (including other intermediate files):

Linux log:

rpu source:

To generate binaries on your own please refer below steps for generating required images/binaries.

Generating required images/binaries

Steps to build Linux images

Create petalinux project

Run below commands from bash terminal to create petalinux project.

source <petalinux-install-dir>/settings.sh petalinux-create -t project -s <xilinx zcu102/vck190 BSP location> cd <petalinux_proj_dir>

Build petalinux

For Versal:

Configure petalinux to use custom XSA (provided in prebuilt section) and enable the custom user application

petalinux-config --silentconfig --get-hw-description <path to xsa file> petalinux-create -t apps --template install --name myapp --enable

copy apu_script.shand another PL bitfiles (partial.pdi, partial.dtbo, greybox.pdi and greybox.dtbo) to myapp (All files provided in prebuilt section)

cd <petalinux_proj_dir>/project-spec/meta-user/recipes-apps/myapp/files/ cp <dow_dir>/apu_script.sh <dow_dir>/partial.pdi <dow_dir>/partial.dtbo <dow_dir>/greybox.pdi <dow_dir>/greybox.dtbo .

Update myapp.bb (located at project-spec/meta-user/recipes-apps/myapp) as shown below

# # This file is the myapp recipe. # SUMMARY = "Simple myapp application" SECTION = "PETALINUX/apps" LICENSE = "MIT" LIC_FILES_CHKSUM = "file://${COMMON_LICENSE_DIR}/MIT;md5=0835ade698e0bcf8506ecda2f7b4f302" FILESEXTRAPATHS_prepend := "${THISDIR}/files:" SRC_URI = "file://myapp \ file://partial.pdi \ file://partial.dtbo \ file://greybox.pdi \ file://greybox.dtbo \ file://apu_script.sh \ " S = "${WORKDIR}" CFLAGS_prepend = "-I ${S}/include" do_install() { echo "D: ${D}" echo "S: ${S}" install -d ${D}${bindir} install -m 0755 ${S}/myapp ${D}${bindir} install -m 0755 ${S}/partial.pdi ${D}${bindir} install -m 0755 ${S}/partial.dtbo ${D}${bindir} install -m 0755 ${S}/greybox.pdi ${D}${bindir} install -m 0755 ${S}/greybox.dtbo ${D}${bindir} install -m 0755 ${S}/apu_script.sh ${D}${bindir} }Replace rootfs_configfile (provided in prebuilt section) with <petalinux-proj-dir>/project-spec/configs/rootfs_config file

Build the petalinux as shown below

petalinux-build

For ZynqMP:

Use below command to create and enable custom petalinux application

petalinux-config --silentconfig petalinux-create -t apps --template install --name myapp --enable

Copy apu_script.sh (provided in prebuilt section) to myapp folder

cp <dow_dir>/apu_script.sh <petalinux_proj_dir>/project-spec/meta-user/recipes-apps/myapp/files/

Update myapp.bb (located at project-spec/meta-user/recipes-apps/myapp/) as shown below

# # This file is the myapp recipe. # SUMMARY = "Simple myapp application" SECTION = "PETALINUX/apps" LICENSE = "MIT" LIC_FILES_CHKSUM = "file://${COMMON_LICENSE_DIR}/MIT;md5=0835ade698e0bcf8506ecda2f7b4f302" FILESEXTRAPATHS_prepend := "${THISDIR}/files:" SRC_URI = "file://myapp \ file://apu_script.sh \ " S = "${WORKDIR}" CFLAGS_prepend = "-I ${S}/include" do_install() { echo "D: ${D}" echo "S: ${S}" install -d ${D}${bindir} install -m 0755 ${S}/myapp ${D}${bindir} install -m 0755 ${S}/apu_script.sh ${D}${bindir} }Enable ECC in FSBL code:

Create directory <plnx-proj-root>/project-spec/meta-user/recipes-bsp/fsbl/files/ (if not present)

Copy patch file to <plnx-proj-root>/project-spec/meta-user/recipes-bsp/fsbl/files/ (Patch attached in prebuilt section)

Open file <plnx-proj-root>/project-spec/meta-user/recipes-bsp/fsbl/fsbl-firmware_%.bbappend (create if not present)

Add below lines in file:

FILESEXTRAPATHS_prepend := "${THISDIR}/files:" SRC_URI += " file://ecc_fsbl.patch"

Now build petalinux using below command

petalinux-build

Steps to build RPU baremetal (ZynqMP and Versal)

Open Vitis and start with empty application as shown below

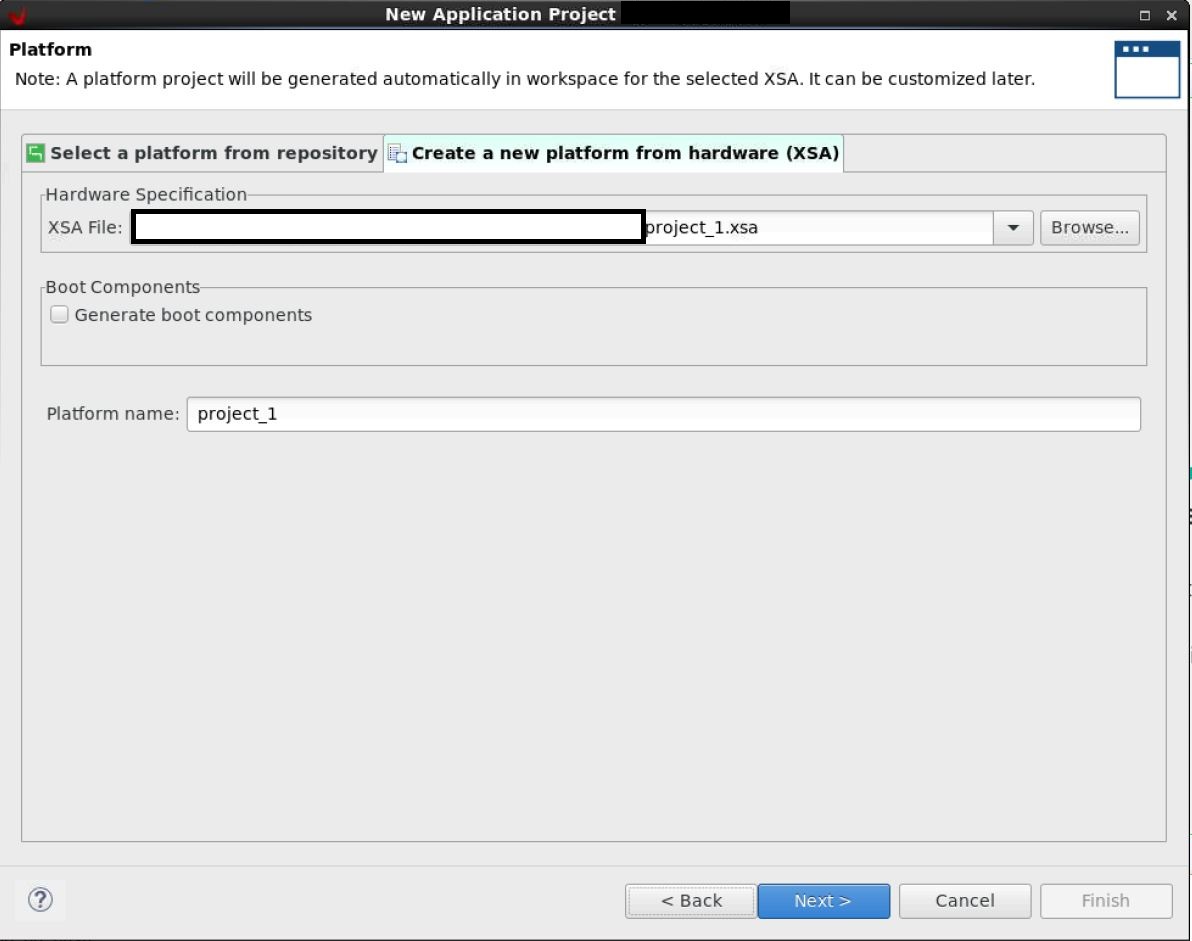

Select “create a new hardware platform“ and select XSA file (petalinux prebuilt XSA for ZynqMP and custom top_wrapper.xsa for Versal from prebuilt secion) as shown below (uncheck generate boot components option in case of ZynqMP)

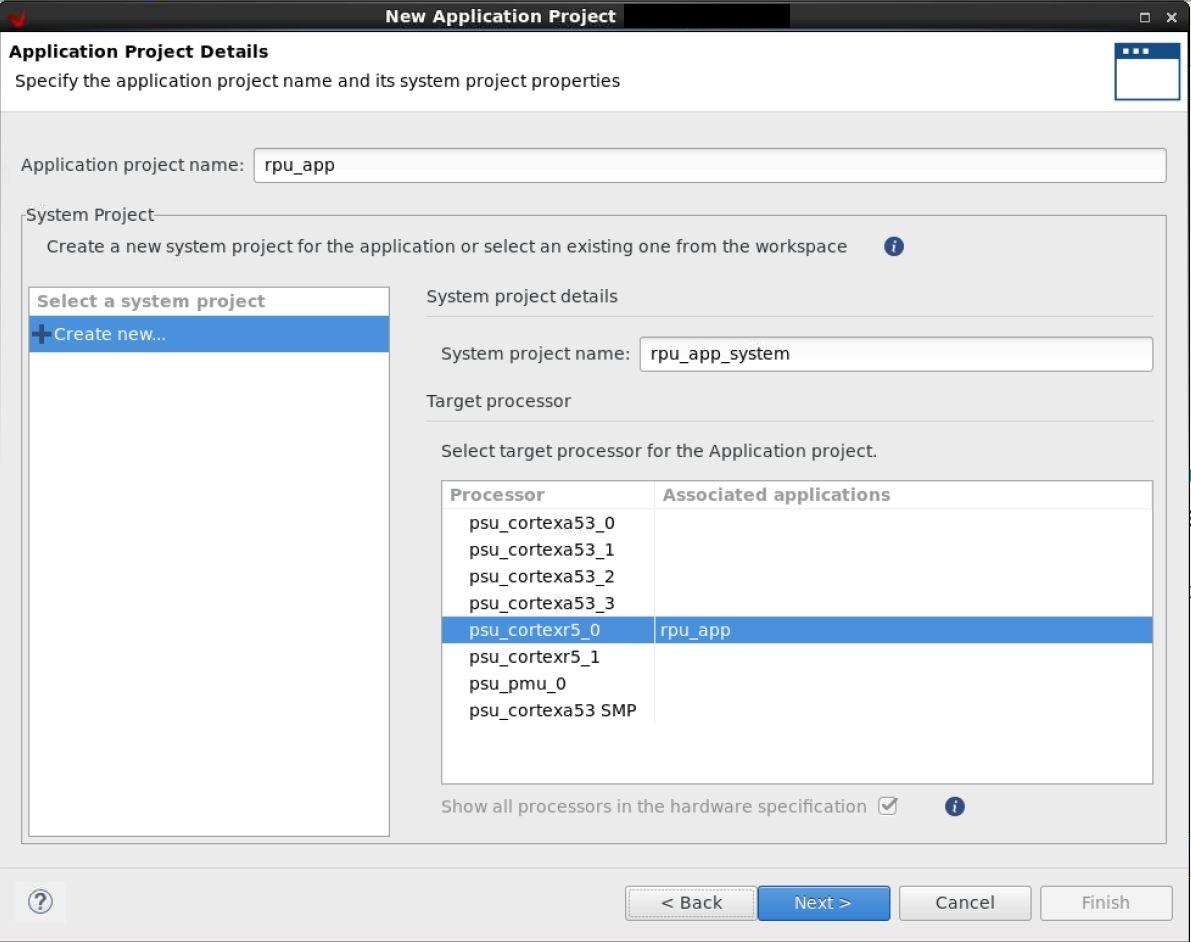

Select target processor as "psu_cortexr5_0" and give the application name (ex. rpu_app)

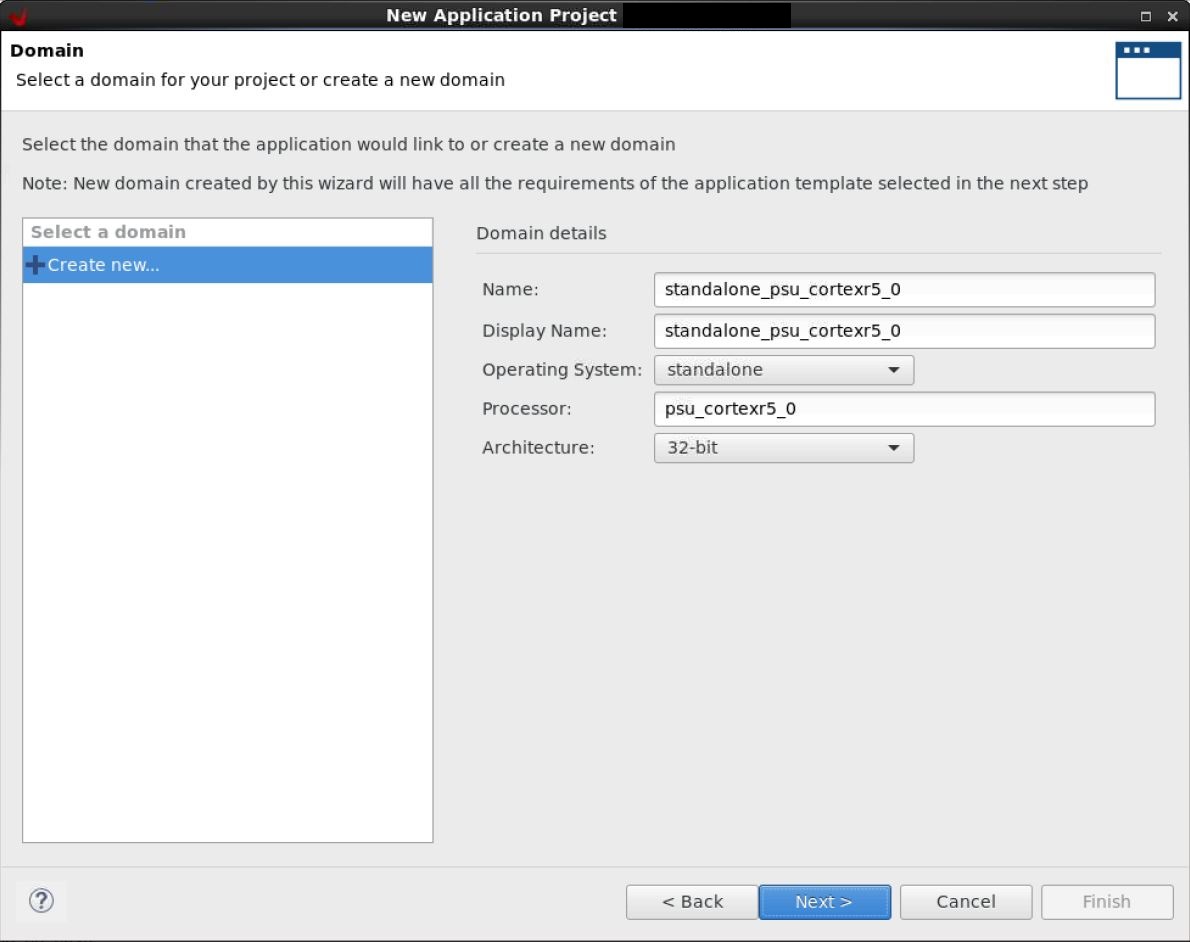

Click next and leave all options unchanged

Click next and select "Empty Application" from the template list

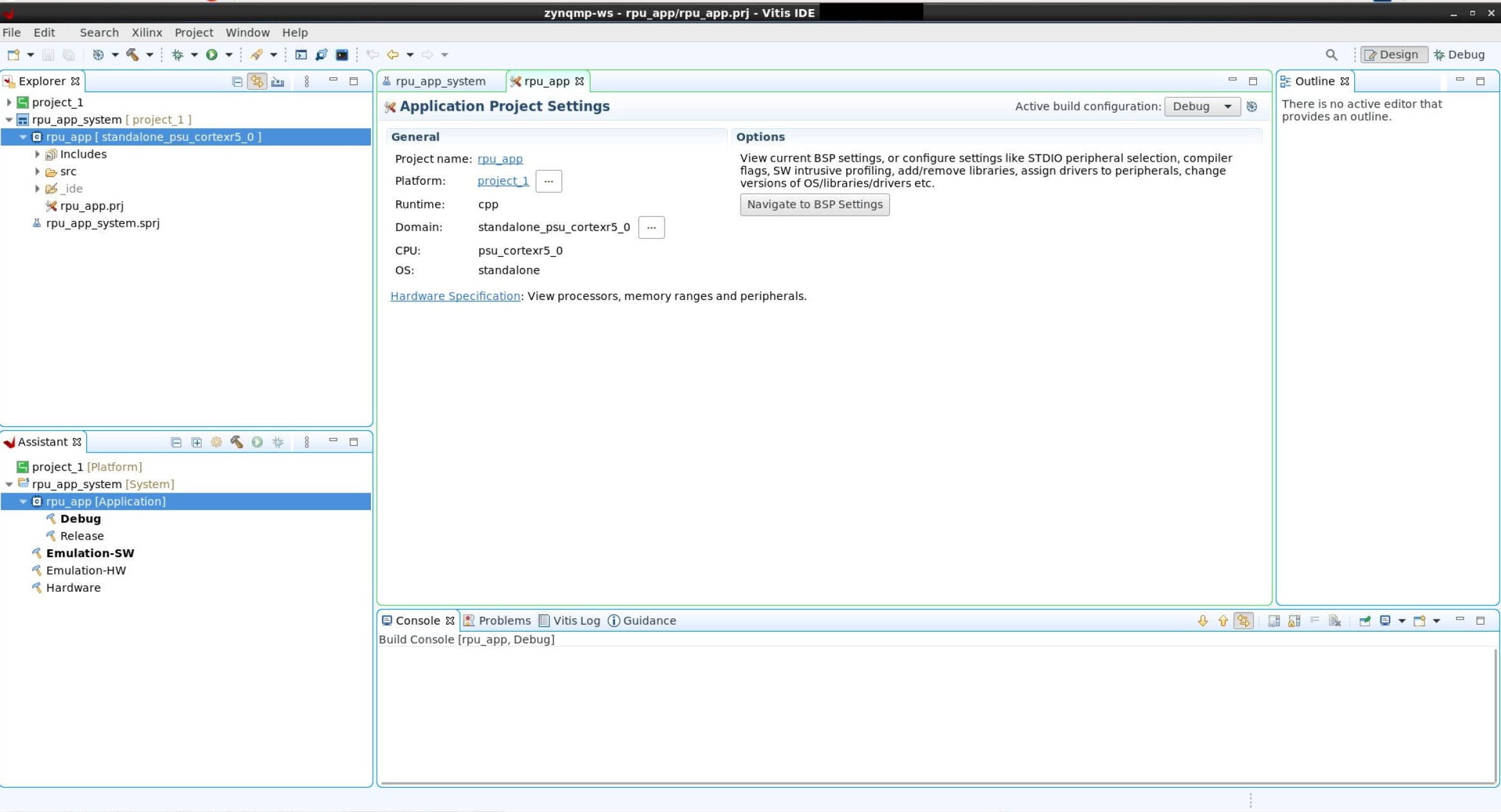

Click finish which will show the project window as shown below

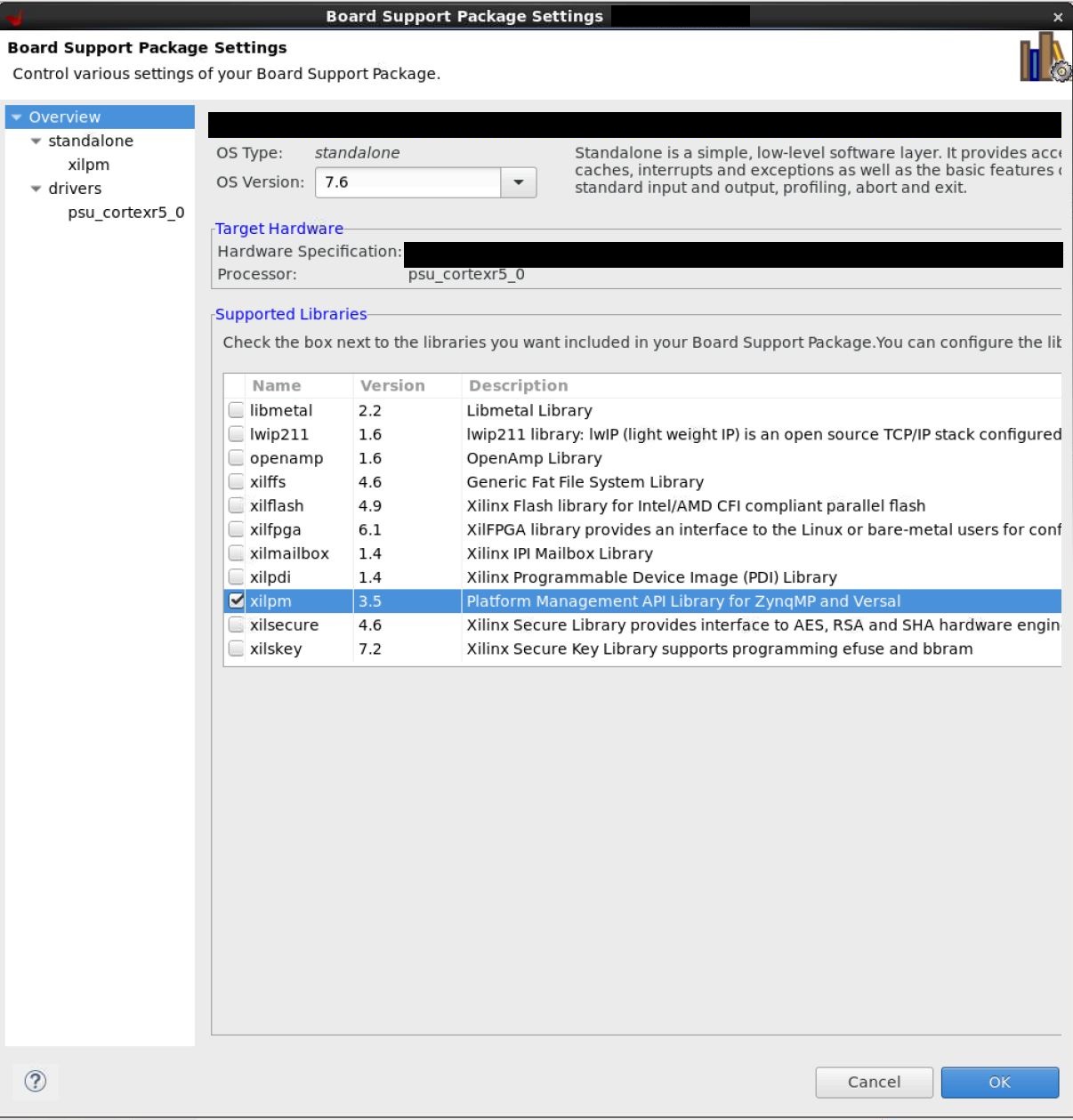

Now click on "Navigate to BSP" settings and click "Modify BSP settings"

Now select the "xilpm" library option as shown below.

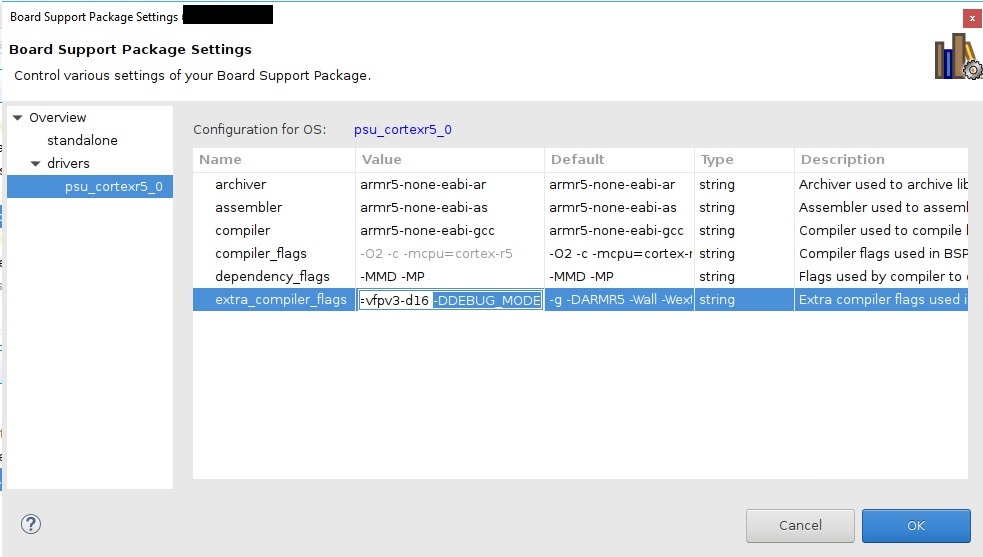

Select psu_cortexr5_0 and add “-DDEBUG_MODE“ in extra_compiler_flags as shown below and click ok.

Right click on "rpu_app" from explorer and select "import sources" option

Download rpu_src.tar and extract it to local folder

Select the source and target path as shown below and click ok

Select yes for overwrite lscript.ld

Right click on "rpu_app" from explorer and select "build project"

Steps to build BOOT.BIN

For ZynqMP

Create a new folder and copy pmufw.elf, zynqmp_fsbl.elf, bl31.elf, u-boot.elf, system.dtb and system.bit from petalinux generated images (present at <plnx-proj-root>/images/linux/).

Create RPU_0 application rpu_app.elf from Vitis as described in above section and copy rpu_app.elf into same new folder.

Create boot.bif file in same folder as shown below.

the_ROM_image: { [bootloader, destination_cpu=a53-0] zynqmp_fsbl.elf [pmufw_image] pmufw.elf [destination_device = pl] system.bit [destination_cpu=r5-0] rpu_app.elf [destination_cpu=a53-0,exception_level=el-3,trustzone] bl31.elf [destination_cpu=a53-0, load=0x00100000] system.dtb [destination_cpu=a53-0,exception_level=el-2] u-boot.elf }Create BOOT.BIN file using following command.

bootgen -arch zynqmp -image boot.bif -w -o BOOT.BIN

For Versal

Create a new folder and copy plm.elf, psmfw.elf, bl31.elf, u-boot.elf and system.dtb from petalinux generated images (present at <plnx-proj-root>/images/linux/).

Copy CDO files (pmc_data.cdo, lpd_data.cdo, fpd_data.cdo, top_wrapper.rnpi, topology_xcvc1902.v3.cdo, topology_board.cdo) present in prebuilt section to same new folder.

Create RPU_0 application rpu_app.elf from Vitis as described in above section and copy rpu_app.elf into same new folder.

Copy boot.bif (present in prebuilt section) to same folder and use below command to create BOOT.BIN

bootgen -arch versal -image boot.bif -w -o BOOT.BIN

Steps to run the images

Boot Linux with RPU

Create a boot partition in SD card and copy BOOT.BIN, Image, system.dtb and rootfs.cpio.gz.u-boot file (present at <plnx-proj-root>/images/linux/) to boot partition.

Boot the board (ZCU102 in case of ZynqMP and VCK190 in case of Versal) in SD boot mode.

Boot the linux from u-boot console using fatload command

fatload mmc 0 0x4000000 system.dtb; fatload mmc 0 0x80000 Image; fatload mmc 0 6000000 rootfs.cpio.gz.u-boot booti 80000 6000000 4000000

Measure the power and transition times

Use Power Advantage tool for measuring power values.

Start the demo

Copy apu_script.sh file from /usr/bin/ and run the script as shown below (For Versal only: also copy partial.pdi, partial.dtbo, greybox.pdi and greybox.dtbo form /usr/bin/ to same folder)

root@xilinx-vck190-2021_2:~# cp /usr/bin/apu_script.sh . root@xilinx-vck190-2021_2:~# cp /usr/bin/partial.* . root@xilinx-vck190-2021_2:~# cp /usr/bin/greybox.* . root@xilinx-vck190-2021_2:~# ./apu_script.sh

Note: User can open the script and edit the below parameters as per his convenient before running script

DelayVal : Amount of delay between 2 power modes (should be between 10 to 255 seconds)

IterationCnt: Total looping count to measure different APU power states latency (should be between 0 to 5Triggering the script starts the demo and it will switch the transition from one state to next dimer state after specific amount of time (default 30 seconds)

User can measure the power readings using power advantage tool between intervals

Latency measurement values is shown as per below window

RPU: Request Suspend Latency of Linux in micro seconds: Min: 99826, Max: 99826, Avg: 99826 RPU: FPD OFF Latency in micro seconds: Min: 6857, Max: 6857, Avg: 6857 RPU: Wakeup Latency of APU0 in micro seconds: Min: 29750, Max: 29750, Avg: 29750 RPU: Wakeup Latency of Linux in micro seconds: Min: 601319, Max: 601319, Avg: 601319 RPU: Latency Measurement Done

Once system reaches to lowest power state, it will starts reverting back to original (normal) power state as shown below

RPU: *********************** RPU ON, APU suspended with FPD OFF ********************** RPU: (50 seconds delay) RPU: (50 seconds RTC timer) RPU: ********************** RPU Idle, APU suspended with FPD OFF ********************* RPU: RTC Alarm generated. RPU: (50 seconds RTC timer) RPU: XPm_SetWakeUpSource(18110005, 18224034, 1, 0, 0) RPU: XPm_SelfSuspend(18110005, FFFF, F, FFE00000, 0) RPU: ******************* RPU Suspended, APU suspended with FPD OFF ******************* RPU: Going to WFI... RPU: Running in lock-step mode RPU: RESUMED RPU: RTC Alarm generated. RPU: *********************** RPU ON, APU suspended with FPD OFF ********************** RPU: (50 seconds delay) RPU: ********************** RPU Idle, APU suspended with FPD OFF *********************

At the end, it will show below completion message (Full log is attached to pre-built images section)

APU: ********************* APU and RPU full load, PL is OFF ************************** APU: Delay 50 seconds APU: Powering on PL domain real 0m0.035s user 0m0.006s sys 0m0.000s [ 812.011953] fpga_manager fpga0: writing partial.pdi to Xilinx Versal FPGA Manager [ 812.042045] OF: overlay: WARNING: memory leak will occur if overlay removed, property: /fpga/firmware-name [ 812.051733] OF: overlay: WARNING: memory leak will occur if overlay removed, property: /__symbols__/overlay0 [ 812.061568] OF: overlay: WARNING: memory leak will occur if overlay removed, property: /__symbols__/fpga_PR0 [ 812.071736] of-fpga-region fpga:fpga-PR0: FPGA Region probed real 0m0.184s user 0m0.017s sys 0m0.060s APU: *********************** APU, RPU and PL in high power *************************** APU: Delay 50 seconds APU: Demo application is completed successfully!

User can re-trigger the apu_script.sh to re-run the demo again.