Zynq UltraScale+ MPSoC Power Advantage Tool part 1 - Introduction to the Power Advantage Tool

Table of Contents

This page provides an introduction to the Power Advantage Tool, as well as links to how to build various components of the Power Advantage Tool and how to make them run on a supported Xilinx Evaluation Board (e.g. ZCU102). The Evaluation Board is based on a Zynq UltraScale+ MPSoC/RFSoC devices (see table below). For additional information, refer to Zynq UltraScale+ MPSoC: ZCU102 Evaluation Kit – Preliminary ZCU102 Getting Started Document.

Information instead on the Versal Adaptive SoC Power Tool can be found here.

Supported Evaluation Boards:

| Board | Device | |

| Ultra96 | XCZU3EG | |

| ZCU102 | XCZU9EG | |

| ZCU106 | XCZU7EV | |

| ZCU111 | XCZU28DR | |

| ZCU208 | XCZU48DR | |

| ZCU216 | XCZU49DR | |

| ZCU670 | XCZU67DR | |

.

1 About the Power Advantage Tool

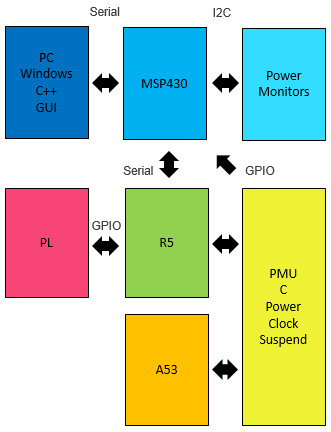

The Power Advantage Tool is a demo designed to showcase the power features of the Zynq UltraScale+ MPSoC device.The Power Advantage Tool consists of four main elements: The Qt PC Windows GUI, the MSP430 Controller code, Zynq UltraScale+ MPSoC R5 code, and the Programmable Logic (PL) design.

(1) The Qt PC GUI provides the user interface for the Power Advantage Tool. The PC communicates to the MSP430, a low-power processor, whose job it is to stay on during the lowest power states of the Zynq UltraScale+ MPSoC, including when the Zynq device is being turned off.

(2) The MSP430 controls the Evaluation Kit Power Monitoring IC’s (INA226’s) and Power Management IC’s (PMICs), as well as communicates with the Zynq UltraScale+ R5.

(3) The R5 is the lowest-power ARM processor on the Zynq UltraScale+ MPSoC, and is on during the lowest power running states. The R5 communicates with the Power Management Unit (PMU) to set the power states, as well as selects the PL Options via GPIO.

(4) The PL contains the Hardware Design.

For additional information, please refer to Power Advantage Tool Theory of Operation.pdf

Figure 1. Power Advantage Tool Block Diagram.

2 Links

Zynq UltraScale+ MPSoC Power Advantage Tool:- Part 1 – Introduction to the Power Advantage Tool

- Part 2 – Installing the Pre-Built Power Advantage Tool

- Part 3 – Running the Pre-Built Power Advantage Tool

- Part 4 – Building and Running the SD Image

- Part 5 – Building and Running the PL Design From Sources

- Part 6 – Building and Running the R5 Design From Sources

- Part 7 – Building and Running the MSP430 Design From Sources

- Part 8 – Building and Running the Qt PC GUI Design From Sources

- Part 9 – Building and Installing the Gimp Artwork From Sources

- Part 10 – Building and Running the Linux Design From Sources

Other References:

- Power Advantage Tool Theory of Operation.pdf

- Power Advantage Tool R5 Theory of Operation.pdf

- Power Advantage Tool Qt Theory of Operation.pdf

- Power Advantage Tool MSP430 Theory of Operation.pdf

- Zynq UltraScale+ MPSoC Ubuntu part 1 - Running the Pre-Built Ubuntu Image and Power Advantage Tool

- Zynq UltraScale+ MPSoC Ubuntu part 2 - Building and Running the Ubuntu Desktop From Sources

3 Prerequisites

- Windows PC with about 40GB free

- 4K Monitor with Display Port Interface (needed only for Ubuntu based demos) (see Xilinx recommended list) Note: HDMI can be substituted for 2017.1, but XaoS Mandelbrot will not display.

- USB Keyboard and Mouse (needed only for Ubuntu based demos)

- Micro USB to USB hub (needed only for Ubuntu based demos)

- Internet Access

- Evaluation board (e.g. ZCU102) and power supply

- 16GB Class 10 SD Card (see Xilinx recommended list) Note: Other than Class 10 is recommended for 2017.1 and 2017.2 builds (e.g. Class 4).

- Cables: Ethernet, DP, (2) Micro USB.

- Vivado License with Vivado System Edition, UltraScale Plus Family with Bitgen (for SD, PL, R5)

- TI MSP-FET (for MSP430 programming)

Note: Boards marked Revision 1.0 or higher come with the MSP430 pre-programmed, and thus the TI cable and TI Code Composer are not required for pre-built image use. Note: The exception is MSP430 version May 17th 2017, which is incompatible.

4 Power Advantage Tool Sources

This section shows how to get and install the Power Advantage Tool Sources. This will be needed for any steps that are Building from Sources.4.1 Download the Power Advantage Tool Sources

An archive with the Power Advantage Tool Sources files zynqus_<Description>_pwr_<Board>_<Datecode>.zip (e.g. zynqus_ubuntu_pwr_20161005.zip) can be downloaded below (requires sign up).4.2 Power Advantage Tool Sources Contents

After you have downloaded the Power Advantage Tool Sources package, extract its contents to C:Figure 2. Power Advantage Tool Sources Directory.

5 Xilinx Vivado and SDK

Optional: This section shows how to get the Xilinx Vivado and SDK tools. These will be needed for any of the steps that Build SD, PL, or R5 from Sources.5.1 Install Xilinx Vivado and SDK

Install Vivado and SDK per instructions on Xilinx.com.Related Links

Home Previous Next© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy