Table of Contents

SD-FEC Driver for Zynq Ultrascale+TM RFSoC

Introduction

This page gives an overview of the Soft-Decision FEC (SD-FEC) driver which is available as part of the Xilinx Linux distribution.

This driver supports the Soft-Decision FEC (SD-FEC) Integrated Block.

The driver is available at

HW IP Features

The HW IP features summary is documented in

SD-FEC Product Guide (PG256)Features supported in driver

- Supports retrieval of the Integrated Block Configuration and Status information

- Supports configuration of LDPC Codes

- Supports configuration of Turbo Decoding

- Monitoring errors

Missing Features, Known Issues and Limitations

- Only allows a single open file handler to any instance of the driver at any time

- Reset of the SD-FEC Integrated Block is not controlled by this driver

- Does not support shared LDPC code table wraparound

- Does not utilizes Linux Clock Control Framework

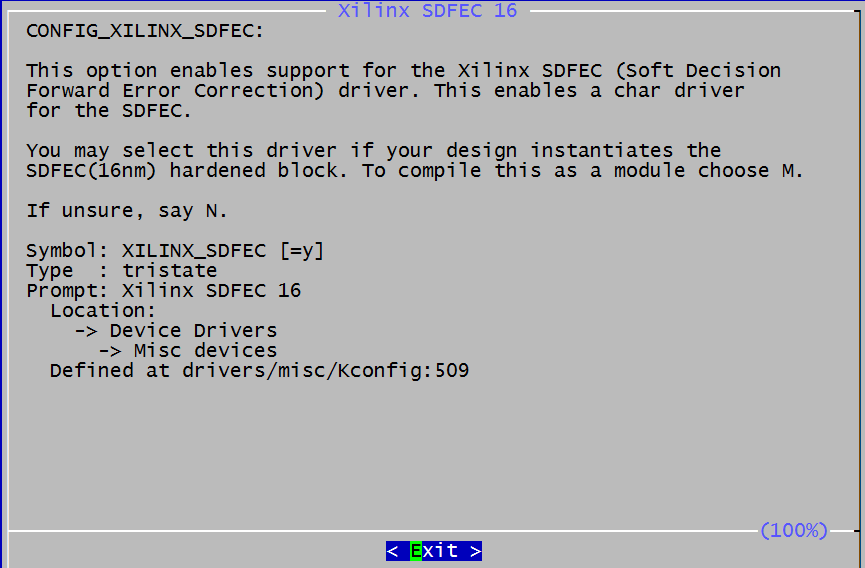

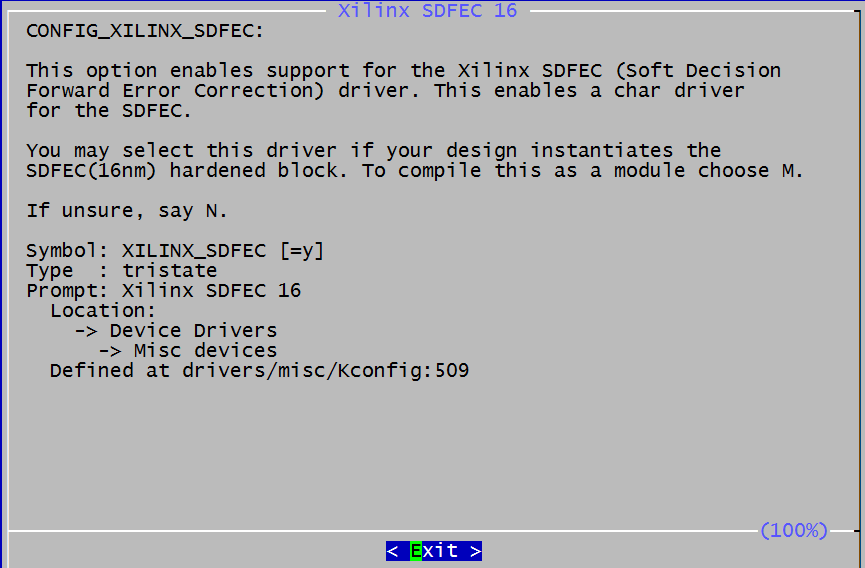

Kernel Configuration

To compile a kernel with a driver for the SD-FEC enable the following kernel config option:

| Code Block |

|---|

|

CONFIG_XILINX_SDFEC |

Device Tree Settings

For more details about the device tree bindings please refer to

https://github.com/Xilinx/linux-xlnx/blob/master/Documentation/devicetree/bindings/misc/xlnx%2Csd-fec.txt . Below is an example of a SD-FEC device tree entry.

| Code Block |

|---|

|

sd_fec_0: sd-fec@a0040000 {

compatible = "xlnx,sd-fec-1.1";

reg = <0x0 0xa0040000 0x0 0x40000>;

interrupt-parent = <&&gic>;

interrupts = <0 89 4>;

xlnx,sdfec-code = "ldpc";

xlnx,sdfec-din-words = <0>;

xlnx,sdfec-din-width = <2>;

xlnx,sdfec-dout-words = <0>;

xlnx,sdfec-dout-width = <1>;

};

|

Driver Examples

LDPC DOCSIS 3.1 Demo Example

This example demonstrates how to set up and control the BER test hardware and to configure a SD-FEC IP instance. It implements an interactive software described in the processor-based example design of SD-FEC Product Guide (PG256).

Source path for the demo is located at:

https://github.com/Xilinx/metalinux-petalinuxexamples/blob/master/relsd-fec-v2018.3/recipes-apps1.1/sdfec-demo/files/main.c

And uses the SD-FEC user interface library located at https://github.com/Xilinx/meta-petalinux/tree/rel-v2018.3/recipes-libs/libsdfecusrintf

To create images that can be deployed using an SD-CARD

- Create petalinux project using the following command:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

$ petalinux-create -t project -s <xilinx-zcu111-v2018v2019.32-final.bsp> -n plnx_sdfec_demo |

Note: xilinx-zcu111-v2018v2019.32-final.bsp is the PetaLinux BSP for ZCU111 Production Silicon Rev1.0 Board. Use xilinx-zcu111-zu28-es1-v2018.3-final.bsp, if board has ES1 Silicon.

- Change to the PetaLinux project directory using the following command:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

$ cd plnx_sdfec_demo |

- Build the Linux images using the following command:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

$ petalinux-build |

- After the above statement executes successfully, verify the images and the timestamp in the images directory in the PetaLinux project folder using the following commands:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

$ cd images/linux/

$ ls -al |

- Generate the Boot image using the following command:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

$ petalinux-package --boot --format BIN --fsbl zynqmp_fsbl.elf --u-boot --fpga system.bit |

The above procedure will create the following SD-Card deployable images

a. BOOT.bin

b. image.ub

Copy the BOOT.BIN and image.ub from plnx-sdfec-demo/plnx_sdfec_demo/images/linux to a SD-CARD.

The following console log demonstrate how to run the SD-FEC demo, to exit the application press CTRL-C.

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

root@xilinx-zcu111-zu28-es1-2018_3:~# sdfec-demo

Initialize all devices

metal: info: metal_uio_dev_open: No IRQ for device a0000000.data_source_top.

metal: info: metal_uio_dev_open: No IRQ for device a0030000.stats_top.

metal: info: metal_uio_dev_open: No IRQ for device a0010000.monitor.

metal: info: metal_uio_dev_open: No IRQ for device a0020000.monitor.

metal: info: metal_uio_dev_open: No IRQ for device a00d0000.monitor.

metal: info: metal_uio_dev_open: No IRQ for device a00e0000.monitor.

Open FECs

Setup LDPC code for decoder

Setup LDPC code for encoder

Start decoder FEC

Start encoder FEC

Setup data source, stats and monitors

Wait for finish

Collect stats

---- RESULTS ----

Stats:

Decode iteration count = 800

Channel bit error count = 12079

Channel block error count = 100

Uncorrected bit error count after Decode = 13763

Uncorrected block error count after Decode = 100

Encoder Monitors:

In Monitor First Timestamp = 2567215315

In Monitor Last Timestamp = 2567216973

In Monitor Num Stalled Clk Cycles = 965

Out Monitor First Timestamp = 2567215410

Out Monitor Last Timestamp = 2567217229

Out Monitor Num Stalled Clk Cycles = 201

Decoder Monitors:

In Monitor First Timestamp = 2567215536

In Monitor Last Timestamp = 2567229792

In Monitor Num Stalled Clk Cycles = 3026

Out Monitor First Timestamp = 2567215966

Out Monitor Last Timestamp = 2567230706

Out Monitor Num Stalled Clk Cycles = 863

Stop encoder FEC

Stop decoder FEC

Current config:

code : 0

num_blocks : 100

snr : 6.000000

max_iter : 8

term_on_pass: 0

mod_type : 2

zero_data : 0

skip_chan : 0

New config? (y/n):y

Input new config:

code: 1

num_blocks: 100

snr:

Next config:

code : 1

num_blocks : 100

snr : 6.000000

max_iter : 8

term_on_pass: 0

mod_type : 2

zero_data : 0

skip_chan : 0

Setup LDPC code for decoder

Setup LDPC code for encoder

Start decoder FEC

Start encoder FEC

Setup data source, stats and monitors

Wait for finish

Collect stats

---- RESULTS ----

Stats:

Decode iteration count = 800

Channel bit error count = 73550

Channel block error count = 100

Uncorrected bit error count after Decode = 77466

Uncorrected block error count after Decode = 100

Encoder Monitors:

In Monitor First Timestamp = 1521568905

In Monitor Last Timestamp = 1521580327

In Monitor Num Stalled Clk Cycles = 7462

Out Monitor First Timestamp = 1521569258

Out Monitor Last Timestamp = 1521580825

Out Monitor Num Stalled Clk Cycles = 0

Decoder Monitors:

In Monitor First Timestamp = 1521569735

In Monitor Last Timestamp = 1521661054

In Monitor Num Stalled Clk Cycles = 40781

Out Monitor First Timestamp = 1521571430

Out Monitor Last Timestamp = 1521665176

Out Monitor Num Stalled Clk Cycles = 0

Stop encoder FEC

Stop decoder FEC

Current config:

code : 1

num_blocks : 100

snr : 6.000000

max_iter : 8

term_on_pass: 0

mod_type : 2

zero_data : 0

skip_chan : 0

New config? (y/n): |

Change Log

2019.1

Commits:

1076693 - misc: xilinx-sdfec: Include doc in TOC

a2aeab2 - misc: xilinx-sdfec: Rename return value

d835d0d - misc: xilinx-sdfec: Apply appendix _MASK

629478d - misc: xilinx-sdfec: Post review document update

7186bc2 - misc: xilinx-sdfec: Correct parameter range check

e532d98 - misc: xilinx-sdfec: Correct an error handling

7ded866 - misc: xilinx-sdfec: Correct integer comparison

2e9d5ef - misc: xilinx-sdfec: Remove not needed ORDER enums

82eb00f - misc: xilinx-sdfec: Remove not needed CODE enums

2fc0d02 - misc: xilinx-sdfec: Realign ioctl magic numbers

ae312a9 - misc: xilinx-sdfec: Remove not used parameters

28e6af0 - misc: xilinx-sdfec: Update after clang-format

498c280 - misc: xilinx_sdfec: Add support for CCF

e588573 - dt: bindings: misc: xilinx_sdfec: Add clock descriptions

4659da9 - MAINTAINERS: Add entry for Xilinx SD-FEC controller

...