This page gives an overview of the bare-metal driver support for the Xilinx® LogiCORE™ IP AXI USB soft IP.

...

| Table of Contents |

|---|

Introduction

The AXI USB device IP is a USB device controller IP. It has no support for OTG mode. This IP can be instantiated on FPGA or Zynq or ZynqMP PL. This page describes the usage of AXI USB device IP standalone driver.

https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/usb/

...

Refer to the driver examples directory for various example applications that exercise the different features of the driver. Each application is linked in the table below. The following sections describe the usage and expected output of the various applications. These example applications can be imported into the Vitis IDE from the Board Support Package settings tab.

Links to Examples

Examples Path:

https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/usb/examples

Test Name | Example Source | Description |

|---|---|---|

| USB Mass-Storage Gadget - Poll Mode | This example does a basic read and writes test from the USB drive in polled mode. |

Example Application Usage

Mass-Storage: USB Polled/Interrupt mode example

Mass storage profile can be tested by compiling xusb_storage_polled_mode.c,xusb_cp9.c,xusb_cp9.h,xusb_storage.h,xusb_types.h,

files together

USB 2.0 Peripheral Mode

The below gives the testing procedure of axi-usb device standalone example which operates as a mass storage gadget

Testing procedure

...

https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/usb/examples

Below is the testing procedure of AXI USB standalone example which operates as a mass storage gadget

- Download and run the generated USB 2.0 example ELF

- Connect board setup to standard host(Windows/Linux)machine USB 2.0 port.

Expected Output

- You will get a pop-up window on a Windows machine for formatting the size 256MB. After the format completes, you can copy the file to the USB device.

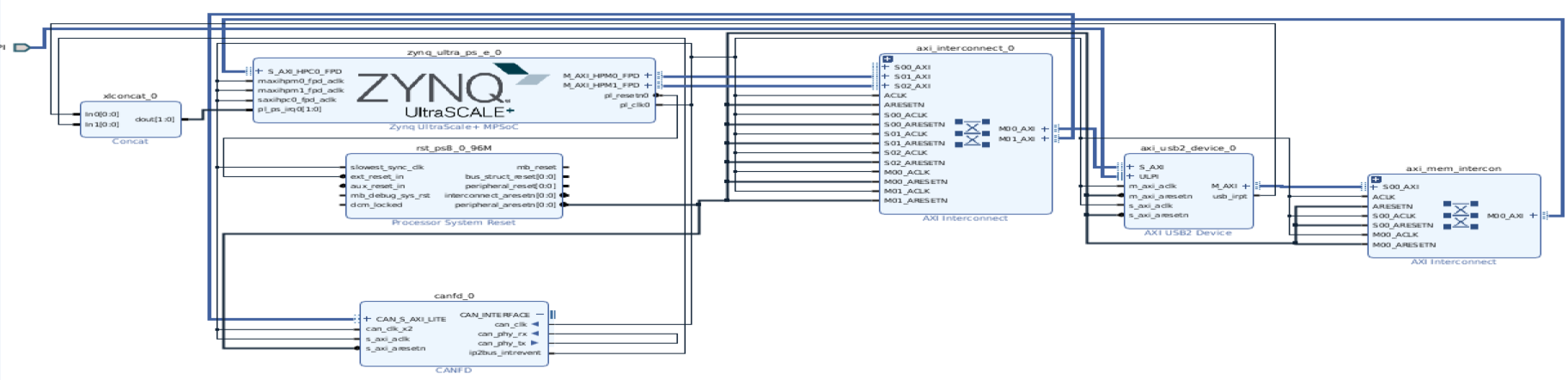

Example Design Architecture

AXI-USB specific design. This is the customized image of axi-usb and canfd. AXI Interconnect module connected with ULPI.

Performance

The below performance results are observed using CrystalDiskMark tool on windows

Change Log

2021.2

- None

2021.1

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2021.1/doc/ChangeLog#L2220

2020.2

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2020.2/doc/ChangeLog#L715

2020.1

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2020.1/doc/ChangeLog#L557

2016.2

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2016.2/doc/ChangeLog#L43

2016.1

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2016.1/doc/ChangeLog#L387

...