This page presents the MTS Design example for ZCU1275/ZCU1285 device.

Table of Contents

| Table of Contents | ||

|---|---|---|

|

ZCU1275/ZCU1285 Build and Run Flow Tutorial

The below sections describe the build and run flow tutorial.

The design package for ZCU1275/ZCU1285 16X16 can be found at the following links:

Vivado Build Flow

Refer to the Vivado Design Suite User Guide: Using the Vivado IDE, UG893, for setting up Vivado environment.

To build the hardware design, execute the following steps

On Windows

- Open a Vivado Tool.

- Navigate to the package folder path and change the directory to ../pl/MTS-IQ folder for MTS IQ design.

- On the Tcl Console of the tool, type

source ./scripts/create_project.tcl

On Linux

Set $DCET_HOME environment variable as given below for linux environment.

| Code Block |

|---|

% export DCET_HOME=</path/to/download/zipfile>/rdf0xxx-zc1275-RFdc-16x16-mts-design-2018-3 |

- Open a Linux terminal.

- Change directory to $DCET_HOME/pl/MTS-IQ folder for MTS IQ design.

- To create the Vivado IPI project and invoke the UI, run the following command.

| Code Block |

|---|

% vivado -source scripts/create_project.tcl |

After executing the script on windows/linux systems, the vivado IPI block design comes up as shown in the following figure.

4. Click the "Generate Bitstream" on left hand side of Vivado Project Panel.

| Note |

|---|

If the user gets any pop-up with "No implementation Results available". Click "Yes". Then, if any pop-up comes up with "Launch runs", Click "OK". |

The design is implemented, and a pop-up window comes up saying "Open Implemented Design". Click "OK".

Below figure depicts the view of opened implemented design.

| Note |

|---|

The actual results might graphically look different than the image shown. |

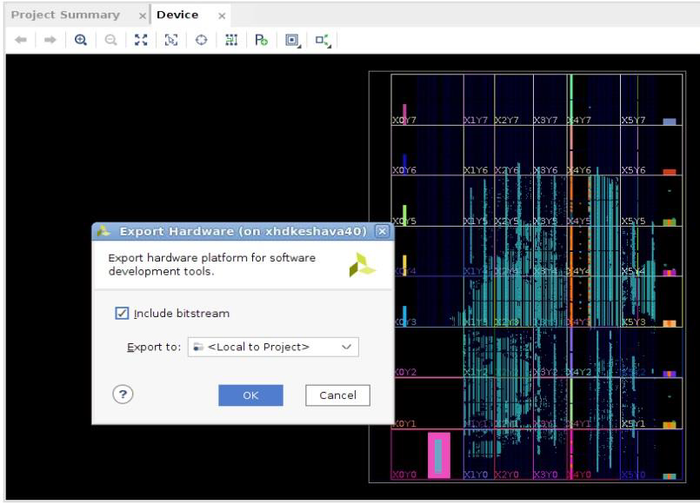

5. Go to File > Export > Export Hardware

6. In the Export Hardware Platform for SDK window select "Include bitstream" and click "OK".

The HDF is created at $DCET_HOME/pl/MTS-IQ/project/zc1275_mts_design.sdk/zc1275_mts_design_wrapper.hdf for MTS IQ Design.

...

- RFTOOL application patch

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/rftool/rftool.bb |

- RFTOOL-MTS application patch

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/rftool-mts/rftool-mts.bb |

- TRD Autostart patch information

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/trd-autostart/trd-autostart.bb |

- RFDC Self-test application changes

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/rfdc-examples/rfdc-selftest_%.bbappend SRC_URI_append = " \ file://0001-selftest_example-change-default-frequency.patch \" |

- RFDC Read-Write application changes

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/rfdc-examples/rfdc-read-write_%.bbappend |

- Device Tree Changes

The changes required with respect to pl memory nodes in kernel version 5.4 have been updated in the following path.

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/device-tree/files/pl-custom.dtsi |

The changes required with respect to contiguous memory allocation (CMA size) are updated in the following path.

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/device-tree/files/system_user.dtsi |

| Note |

|---|

To get "project-spec/meta-user/" folder, please extract files from. bsp using step #3 from section PetaLinux build Flow . |

Modifications on top of 2021.1 released BSP

Below are the modification in this TRD for linux-kernel, rftool and rftool-mts applications, on top of 2021.1 petalinux released BSP.

For more details on patch information please refer to http://xkb/Pages/72/72417.aspx.The High level description is given below:

- Kernel patch information

| Code Block |

|---|

% vim project-spec/meta-user/recipes-kernel/linux/linux-xlnx_%.bbappend

SRC_URI_append = " \

file://0001-power-supply-irps-Add-support-for-irps-supply.patch \

file://0002-drivers-misc-add-support-for-DDR-memory-management.patch \

file://0003-dmaengine-xilinx_dma-In-SG-cyclic-mode-allow-multipl.patch \

file://0004-drivers-misc-add-support-for-selecting-mem-type.patch \

file://0005-i2c-cadence-Implement-timeout.patch \

file://0006-drivers-misc-change-ADC-packet-size-as-per-FIFO-size.patch \

file://0007-drivers-misc-change-parameters-for-of_dma_configure.patch \

file://0008-plmem-clean-up-sysfs-node-and-character-device-nodes.patch \

file://0009-dma-clean-the-BD-s-only-when-done-bit-is-set.patch \

file://0010-misc-plmem-replace-dma_declare_memory-with-reserved-.patch \

file://0011-drivers-misc-add-16x16-dac-adc-support.patch \

file://0012-DMA-changes-as-per-kernel-v5_10.patch \ " |

- RFTOOL application patch

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/rftool/rftool.bb |

- RFTOOL-MTS application patch

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/rftool-mts/rftool-mts.bb |

- TRD Autostart patch information

| Code Block |

|---|

% vim project-spec/meta-user/recipes-apps/trd-autostart/trd-autostart.bb |

- RFDC Self-test application changes

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/rfdc-examples/rfdc-selftest_%.bbappend SRC_URI_append = " \ file://0001-selftest_example-change-default-frequency.patch \" |

- RFDC Read-Write application changes

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/rfdc-examples/rfdc-read-write_%.bbappend |

- Device Tree Changes

The changes required with respect to pl memory nodes in kernel version 5.10 have been updated in the following path.

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/device-tree/files/pl-custom.dtsi |

The changes required with respect to contiguous memory allocation (CMA size) are updated in the following path.

| Code Block |

|---|

% vim project-spec/meta-user/recipes-bsp/device-tree/files/system_user.dtsi |

| Note |

|---|

To get "project-spec/meta-user/" folder, please extract files from. bsp using step #3 from section PetaLinux build Flow . |

Run Flow

Clock Configuration for running the design

...

After exiting the application ADC_DATA.csv file is copied in the SD card.

Remove the SDcard and plot the ADC content in Excel sheet.

Find below reference plot for IQ data capture. As can be seen in the plot all the signal sent through DACs and received through ADCs are aligned.

| Note |

|---|

Excel can not plot waveforms for larger sample sizes. The examples given below are for 1K sample. Based on number of samples that can be plotted please select appropriate number of sample sizes (Excel rows) from .CSV file. For observing larger sample sizes please use .CSV compliant tools like Matlab or equivalent. |

The below snapshot shows the code snippet to plot data in MATLAB using the .CSV file

IQ Data Capture (90 degree phase shift between I and Q components)

...