Emaclite Standalone Driver

Ethernetlite driver is in minimal support mode and will be deprecated shortly

Table of Contents

Introduction

The AXI Ethernet Lite core is a soft Xilinx IP core for use with the Xilinx Vivado® Design Suite. The Xilinx® LogiCORE™ IP AXI Ethernet Lite Media Access Controller (MAC) core is designed to incorporate the applicable features

described in the IEEE Std. 802.3 Media Independent Interface (MII) specification. It communicates with the processor using the AXI4 or AXI4-Lite interface. The core supports a 10 Mb/s and 100 Mb/s (also known as Fast Ethernet) interface.

For more information, please refer to the AXI Ethernet Lite product page which includes links to the official documentation and resource utilization.

Driver Sources

The source code for the driver is included with the Vitis Unified Software Platform installation, as well as being available in the Xilinx Github repository.

| Driver Name | Path in Vitis | Path in Github |

|---|---|---|

| emaclite | <Vitis Install Directory>/data/embedded/XilinxProcessorIPLib/drivers/emaclite_<version> | https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/emaclite |

Note: To view the sources for a particular release, use the rel-version tag in github. For example, for the 2020.1 release, the proper version of the code is: https://github.com/Xilinx/embeddedsw/tree/xilinx-v2020.1/XilinxProcessorIPLib/drivers/emaclite

The driver source code is organized into different folders. The table below shows the emaclite driver source organization.

| Directory | Description |

|---|---|

| doc | Provides the API and data structure details |

| data | Driver .tcl,.mdd file and .yaml files |

| examples | Example applications that show how to use the driver features |

| src | Driver source files, make and cmake files |

Note: AMD Xilinx embeddedsw build flow is changed from 2023.2 release to adapt to the new system device tree based flow. For further information, refer to the wiki page Porting embeddedsw components to system device tree (SDT) based flow - Xilinx Wiki - Confluence (atlassian.net).

The .yaml(in data folder) and CMakeLists.txt(in src folder) files are needed for the System Device Tree based flow. The Driver .tcl and .mdd files are for the older build flow which will be deprecated in the future.

Driver Implementation

For a full list of features supported by this IP, please refer to the AXI Ethernet Lite product page.

Features

The AXI Emaclite Standalone driver supports the following features: - Supports Internal loopback mode

- Supports Ping pong buffers for both RX and TX

- Supports MII for connection to external 10/100 Mbps PHY transceivers

- Supports accessing of PHY through MDIO interface.

Known Issues and Limitations

- Driver is validated only on Microblaze based platforms and not validated/maintained on ARM designs

Example Design Architecture

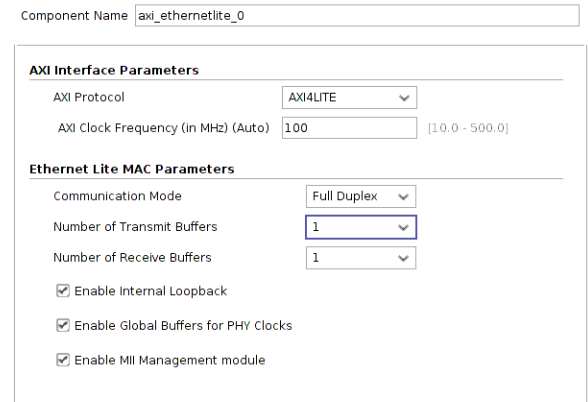

The examples assumes AXI Ethernet IP has number of TX and RX buffer=1 , Internal loopback and MII management module is enabled. For interrupt examples interrupt controller should be connected to processor.

Example Applications

Refer to the driver examples directory for various example applications that exercise the different features of the driver. Each application is linked in the table below. The following sections describe the usage and expected output of the various applications. These example applications can be imported into the Vitis IDE from the Board Support Package settings tab.

Links to Examples

Examples Path: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/emaclite/examples

| Test Name | Example Source | Description |

|---|---|---|

| Self Test | xemaclite_selftest_example.c | This example performs the self-test on the emaclite device example does a write to Tx buffer and read back's to verify similarly write to Rx buffer and read back's to verify. |

| Internal loopback | xemaclite_internal_loopback_example.c | This is an interrupt example outlines the use of interrupts and callbacks in the transmission/reception of Ethernet frames using internal loopback with an incrementing payload from 1 byte to 1500 bytes (excluding Ethernet Header and FCS). |

| Frame transfer with interrupts | xemaclite_intr_example.c | This interrupt example outlines the use of interrupts and callbacks in the transmission/reception of an Ethernet frame of 1000 bytes of payload. If the MDIO interface is NOT configured in the EmacLite core then this example will transmit a frame. If the MDIO interface is configured in the EmacLite core then this example will enable the MAC loopback in the PHY device, then transmit the frame and compare the received frame. |

| Frame transfer with polling | xemaclite_polled_example.c | This polled mode example outlines the transmission/reception of an Ethernet frame of 1000 bytes of payload. If the MDIO interface is NOT configured in the EmacLite core then this example will transmit a frame. If the MDIO interface is configured in the EmacLite core then this example will enable the MAC loopback in the PHY device, then transmit the frame and compare the received frame. |

| PHY loopback | xemaclite_phy_loopback_example.c | This is an interrupt example outlining the use of interrupts and callbacks in the transmission/reception of Ethernet frames using MAC loop back in the PHY device with an incrementing payload from 1 byte to 1500 bytes (excluding Ethernet Header and FCS). |

| Ping request | xemaclite_ping_req_example.c | This is an EmacLite Ping request example in polled mode. This example will generate a ping request for the specified IP address. |

| Ping reply | xemaclite_ping_reply_example.c | This is an EmacLite ping reply example in polled mode. This example will generate a ping reply when it receives a ping request packet from the external world. |

Example Application Usage

Self Test

This example performs the self-test on the emaclite device example and does a write/read on Tx and Rx ping pong buffers.

Expected Output

Successfully ran Emaclite selftest Example

Internal loopback

This is an interrupt example outlining the use of interrupts and callbacks in the transmission/reception of Ethernet frames using internal loopback with an incrementing payload from 1 byte to 1500 bytes.

NOTE- In internal loopback mode, the AXI Ethernet Lite MAC core routes back data on the TX lines to the RX lines.

Expected Output

Successfully ran Emaclite internal loopback Example

Frame transfer with interrupts

This example demonstrates how to transfer packets with interrupts in emaclite phy loopback mode.

Expected Output

Successfully ran Emaclite interrupt Example

Frame transfer with polling

This example demonstrates how to transfer packets with polling in emaclite phy loopback mode.

Expected Output

Successfully ran Emaclite polled Example

PHY loopback

This example demonstrates how to transfer packets with interrupts in emaclite phy loopback mode. If MDIO is not configured a failure is returned.

Expected Output

Successfully ran Emaclite phy loopback Example

Ping request

This example generate a ping request for the specified IP address.

Expected Output

Successfully ran Emaclite ping request Example

Ping reply

This example generate a ping reply when it receives a ping request packet from the external world.

Expected Output

Successfully ran Emaclite ping reply Example

Change Log

2024.1

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2024.1/doc/ChangeLog#L393

2023.2

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2023.2/doc/ChangeLog#L557

2022.1

None

2021.1

None

2020.2

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2020.2/doc/ChangeLog#L439

2020.1

None

2019.2

None

Related Links

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy