Xilinx V4L2 VPSS Scaler driver

Table of Contents

Introduction

The purpose of this page is to describe the Linux V4L2 driver for Xilinx VPSS Scaler soft IP. VPSS refers to the Video Processing Sub System.

To understand more about the capabilities of this IP please see the Product Guide (Scaler Only configuration) for VPSS.

To understand more about the capabilities of this IP please see the Product Guide (Scaler Only configuration) for VPSS.

The Linux VPSS Scaler driver (xilinx-vpss-scaler.c) based on the V4L2 framework creates a subdev node(/dev/v4l-subdev*) which can be used to configure the VPSS Scaler IP core. The V4L2 VPSS Scaler driver controls the VPSS Scaler soft IP to achieve upscaling and downscaling of Video and it also provides certain color space conversions. The driver is available at https://github.com/Xilinx/linux-xlnx/blob/master/drivers/media/platform/xilinx/xilinx-vpss-scaler.c

IP/Driver Features

| IP features | 2018.1 to 2018.3 | 2019.1 | 2019.2 - 2021.2 |

|---|---|---|---|

| IP version | 2.0 | 2.2 | |

| One, two or four pixel-wide AXI4-Stream video interface | Yes* | Supports 1,2,4 and 8 ppc Driver supports 1,2 and 4 | |

| Video resolution support up to UHD at 60 fps | Yes | ||

| 8, 10, 12, and 16 bits per component support | Driver supports only 8 and 10 bpc formats using only 8 bpc MEDIA BUS formats. | Yes** Driver supports only 8 and 10 bpc formats using 8 and 10 bpc media bus formats | Yes** Driver supports only 8 and 10 bpc formats using 8 and 10 bpc media bus formats |

| Bilinear, Bicubic and polyphase algorithms supported. | Yes*** | ||

Missing Features / Known Issues / Limitations in Driver

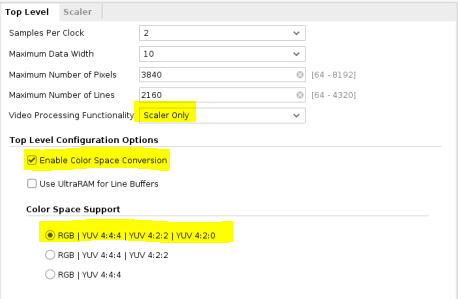

- Colorspace support options are limited to only RGB | YUV 4:4:4 | YUV 4:2:2 | YUV 4:2:0. All other colorspace options are not supported in this release.

- *The maximum samples per clock supported by the Linux Driver is 1 and 2 (also called pixels per clock). 4 pixels per clock is not supported.

- **12 and 16 bit color depth is not supported by this driver.

- **Maximum color depth supported by the VPSS Scaler soft IP driver is limited to 8-bit and 10-bit in this release.

- ***Asymmetrical scaler taps are not supported. Horizontal taps must be same as Vertical taps.

- Fixed coefficients are used in the driver. In future, this may be an input from application.

Video Processing Subsystem Release Notes and Known Issues

Kernel Configuration

CONFIG_VIDEO_XILINX_VPSS_SCALER and CONFIG_VIDEO_XILINX should be enabled.

https://github.com/Xilinx/linux-xlnx/blob/master/Documentation/devicetree/bindings/media/xilinx/xlnx%2Cv-vpss-scaler.txt

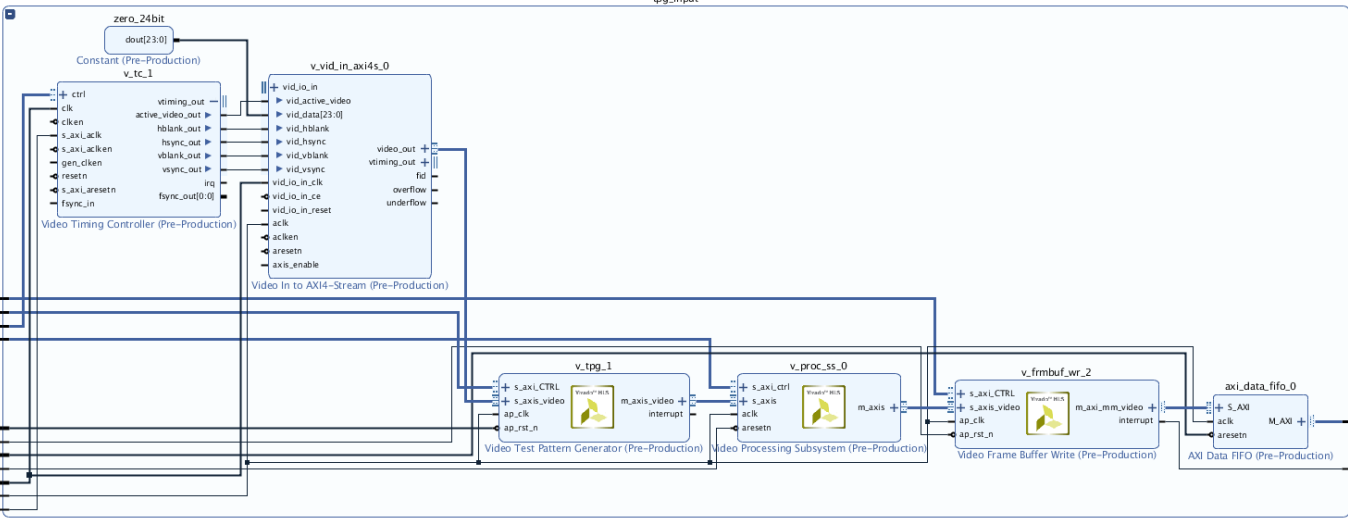

a DMA element (like Framebuffer Write IP). The V4L2 device driver for this IP cannot be tested in isolation by itself. The successful operation of the driver can be tested in two phases :

media-ctl allows you to print the topology of your media pipeline and specify input and output pad properties.

Device Tree Binding

The dts node should be defined with correct hardware configuration. How to define the node is documented here:https://github.com/Xilinx/linux-xlnx/blob/master/Documentation/devicetree/bindings/media/xilinx/xlnx%2Cv-vpss-scaler.txt

Testing Procedure

This driver is a V4L2 sub-device driver, which means it is designed to operate with a video device in it's graph. The driver has been tested with a Xilinx video device (a V4L2 capture device) that is backed bya DMA element (like Framebuffer Write IP). The V4L2 device driver for this IP cannot be tested in isolation by itself. The successful operation of the driver can be tested in two phases :

- Successful Creation of a Media Device

- Successful Frame Captures (or writing of buffers by the Frame-buffer Write IP)

Successful Creation of a Media Device

media-ctl is a Linux user space utility that can control media entities, it is a part of a larger set of V4L2 tools called v4l-utilsmedia-ctl allows you to print the topology of your media pipeline and specify input and output pad properties.

Successful Frame Captures

Please see the Test Approach section of the Frame Buffer Write Wiki for more details on how to capture frames.

The driver has been tested with a design having TPG + VTC feeding video to VPSS Scaler connected to Framebuffer Write.

/* Setup TPG color bar pattern */ media-ctl -v -V '"a3c30000.tpg":0 [fmt:RBG24/1920x1080 field:none]' media-ctl -v -V '"a3c40000.csc":1 [fmt:RBG24/1280x720 field:none]' yavta -n3 -c15 -f RGB24 -s1280x720 --skip 12 -F /dev/video0

Frame Scaling or Resizing:

This media-ctl and yavta commands capture frames down scaled from 1920x1080 to 1280x720 in RGB888 format.

Scaling using bilinear, bicubic and poly-phase (6, 8, 10 and 12 tap) filters that use coefficients programmed by the driver.

Color Space Conversion. All color space conversions have been tested.

#VPSS: Scaler Only with CSC Upscale from 720p to 1080p and changing the color space from RGB to YUV 4:2:0 media-ctl -d /dev/media7 -V '"a0080000.v_proc_ss":0 [fmt:RBG888_1X24/1280x720 field:none]' media-ctl -d /dev/media7 -V '"a0080000.v_proc_ss":1 [fmt:VYYUYY8_1X24/1920x1080 field:none]'

Scaling Formats that have been tested are as follow :

| Sr No. | Video Input Resolution | Video Output Resolution |

| 1. | 1280x720 | 1920x1080 |

| 2. | 1280x720 | 3840x2160 |

| 3. | 3840x2160 | 1920x1080 |

| 4. | 640x480 | 1280x720 |

Boards Supported

Driver has been tested on following boards:

- ZCU102 Rev 1.0

- ZCU106 Rev 1.0

Known Issues

- AR65449 - LogiCORE IP Video Processing Subsystem(VPSS) - Release Notes and Known Issues for the Vivado 2015.3 tool and later versions

Change log

2024.1

- No changes

2023.2

- Summary

- Fix Kernel documentation.

- Commits

2023.1

- No Changes

2022.2

- No Changes

2022.1

- No Changes

2021.2

- No changes

2021.1

- No changes

2020.2

- Summary

- Fix Coverity warnings

- Commits

2020.1

- Summary

- Expect better quality output on account of more coefficient tables per scale ratio range

- Commits

2019.2

- Summary

- Add support for 4 ppc

- Add support for v2.2 of IP version (change in HPHASE base address from 0x2000 to 0x4000)

- Commits

2019.1

- Summary

- Add support for 10bpc media bus formats

- Make max-width and max-height mandatory dt properties

- Fix common clock framework support.

- Commits

2018.3

- Summary

- Fix array out of bound access leading to random kernel crash

- Add check for max width and height from device tree

- Commits

2018.2

- No changes

2018.1

- Summary

- Clear the H-phase array to fix repeated pixels seen in up-scaling video

- Add YUV 420 support

- Commits

2017.4

- Summary

- No changes

2017.3

- Summary

- Add initial version of the driver

- Commits

d136f7c v4l: xilinx-vpss-scaler: Fix phase calculation

3f17edf v4l: xilinx-vpss-scaler: fix dev_dbg logging typo and remove dead code

2ae0fd4 v4l: xilinx-vpss-scaler: fix logical error in pixels per clock check

0c99a1e v4l: xilinx-vpss-scaler: add bilinear and bicubic scaling support

ee7f2ef v4l: xilinx-vpss-scaler: driver support for xilinx vpss scaler

Related Links

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy