Zynq-7000 AP SoC - Base TRD execution from 32 Bit ECC Proxy System Tech Tip

Table of Contents

Document History

| Date | Version | Author | Description of Revisions |

| 01/09/14 | 0.1 | Yashu Gosain | Initial revision |

Summary

As technology is evolving, dynamic random-access memory (DRAM) device size increases and components on chips get smaller, due to that DRAM chips becoming more affected by electrical or magnetic interference. Lower energy particles are able to change memory cell’s state. These kinds of interference can cause a single bit of DRAM to spontaneously flip to the opposite state. It can lead system to either crash or to corruption of data.Several approaches have been developed to deal with unwanted bit-flips. One of the approaches is to calculate an error-correcting code (ECC) for data and store it in DRAM along with data. The most common ECC, a SECDED Hamming code, allow a single bit error to be corrected and double bit errors to be detected.

Zynq-7000 SoC only offers 16 bit ECC on DRAM DDR devices which is only the half-bus (16-bit) data width DDR configuration. Several customers prefer to use a single DDR RAM at 32-bits width for data stored in DRAM, but require ECC for software storage in DRAM.

To provide ECC support for 32 bit access in Zynq, a reference design named “ECC proxy” is developed. To get more information about it, refer to ZYNQ7000AP_SoC_ProxyDesign.pdf provided along with design files. Refer to Appendix A for design files structure.

This tech-tip demonstrates execution of Video processing application from 32 bit ECC protected region. For executing video processing application from 32 bit ECC capable memory region, Zynq Base Target reference design (TRD) for 2013.4 is integrated along with 32 Bit ECC proxy system.

This Tech-tip provides detail about base TRD integration with 32 bit ECC proxy system. It also provides steps to port PetaLinux on 32 bit ECC proxy address space. User can reference this integrated design for their customization.

For additional, please refer toUG925: Zynq-7000 SoC: ZC702 Base Targeted Reference Design User Guide.

Application Processer unit (APU) of Zynq-7000 SoC normally accesses external DDR memory via L2 cache. All coherent access from APU goes through Snoop control unit (SCU) which in turn connected to L2-cache controller. There is dedicated port from L2- controller to DDR controller for reducing latency in accessing external DDR memory.

When the ECC proxy is added to the Programmable Logic (PL) as shown below, APU transactions to General purpose Master AXI interface (M_AXI_GP1) are redirected to DDR through the ECC proxy, which adds ECC protection bytes to each data bytes. Data movement to/from DDR will be through High Performance Slave (HP) port.

For Proxy system level details, refer to ZYNQ7000AP_SoC_ProxyDesign.pdf which is provided along with design files under ZYNQ_TRD_PROXY_HOME /doc folder. Appendix A provides details about design files.

To support this system, DDR memory region is divided in following region

In this system, ECC protected region is used as a system memory. This section is used to execute Linux kernel as well as user space application. Linux kernel data and code section resides here.

This memory region is used to store incoming Video data from Test pattern generator (TPG) or HDMI Input. Software Sobel filter application executing from 32 bit ECC protected region, get the video from this memory and process it. After processing, Sobel filter application store processed Video data back to this memory for Display.

Below is PS address space for above mentioned use-case

Above figure depicts M_AXI_GP1 address space from 0x8100000 to 0x97FFFFFF maps to DDR memory space starts from 0x0200_0000 to 0x2FFF_FFFF. This ECC protected region is defined with in the physical system address space with a 1MB granularity.

DDR ECC protected region addresses are expanded by 2x of M_AXI_GP1 ECC protected area. That is for each byte written through M_AXI_GP1 interface is expanded because of additional ECC byte written along with the data byte. So half of the complete ECC protected region in DDR is used for ECC protected data and half for byte level ECC storage.

This section explains how to generate the FPGA hardware bitstream using the Xilinx Vivado tool (version: 2014.1) and how to export the hardware platform to Xilinx Software Development Kit (SDK) for software application development.

Steps for building the FPGA hardware bitstream

The above step creates a project for Zynq 32 bit DDR proxy.

In the Flow Navigator pane on the left-hand side under Program and Debug, click Generate Bitstream. The bitstream will be generated at $ZYNQ_TRD_PROXY_HOME/hardware/vivado/project/zynq_base_trd_2013.4.runs/impl_1/ system_top_wrapper.bit

Steps for exporting the hardware platform to SDK

From the Vivado menu bar, select File > Export > Export Hardware for SDK

In the Export Hardware for SDK window press OK. The SDK hardware platform will be exported to $ZYNQ_TRD_PROXY _HOME/hardware/vivado/project/zynq_base_trd_2013.4.sdk/SDK/SDK_Export

Note: If the Launch SDK option is checked in the Export Hardware window, SDK will be launched immediately after SDK export has completed. This is not recommended at this point.

Precompiled zynq_fsbl.elf is provided along with design file under following directory

ZYNQ_TRD_PROXY_HOME/ready_to_use folder. If user want to use precompiled zynq_fsbl.elf, than skip this section.

Note: The provided FSBL project is a customized version of the FSBL SDK project template. The following features have been edited to support this design:

The build process will start automatically and builds the BSP first and then the FSBL. The generated Zynq FSBL executable can be found at $ZYNQ_TRD_PROXY_HOME/software/workspace/zynq_fsbl/Debug/zynq_fsbl.elf

PetaLinux will be installed in the petalinux-v2013.10-final directory, directly underneath the working directory of this command.

So, if you install the installer into your home directory /home/user, PetaLinux will be installed in /home/user/petalinux-v2013.10-final.

You may move the resulting petalinux-v2013.10-final directory to a preferred location before continuing.

"Xilinx Design Tools: Installation and Licensing Guide (UG798)" section "Obtaining and Managing a License".

e.g.:

The first time the setup script is sourced, it will perform some post installation tasks to check system dependencies and initialize the Linux kernel source tree.Below is an example of the output from sourcing the setup script for the first time:

PetaLinux environment set to ’/home/user/petalinux-v2013.10-final

INFO: Finalizing PetaLinux installation

INFO: Checking free disk space

INFO: Checking installed tools

INFO: Checking installed development libraries

INFO: Checking network and other services

The post-install step only occurs once. Subsequent runs of the settings script should be much quicker, and simply output a confirmation message such as that shown below:

PetaLinux environment set to ’/home/user/petalinux-v2013.10-final'

/home/user/petalinux-v2013.10-final

Environment variable "$PETALINUX" should point to the path to the installed PetaLinux. Your echo output may be different from this example, depending upon where you installed PetaLinux.

PetaLinux includes reference designs for you to start working with and customize for your own projects. These are provided in the form of installable BSP (Board Support Package) files, and include all necessary design and configuration files, including pre-built and tested hardware and software images, ready for download to your board or for booting in the QEMU system simulation environment.

Run petalinux-create command on the command console:

petalinux-create -t project -s <path-to-bsp>

INFO: Create project:

INFO: Projects:

INFO: * zynq_base_trd_2013.4

<snip>

Create a new branch named zynq_base_trd_v2013.4 based on the xilinx-v2013.4-trd tag-t

Select kernel menu in Linux configuration. It opens Kernel selection sub-menu.

Select linux-xlnx kernel. Press Enter.

Select Kernel Base address in Linux Configuration. It opens Kernel base address sub menu

Change following definition and save the file.i

Change memory definition as below and save the file.

memory {

device_type = “memory”;

reg = <0x81000000 0x17000000>;

}

Change following definition and save the file

Run ’petalinux-build’ in the PetaLinux SDK project directory to build the PetaLinux system image

Note: For more verbose build message use PetaLinux-build -v.

The console shows the compilation progress. e.g.:

INFO: Checking component...

INFO: Generating make files and build Linux

INFO: Generating make files for the subcomponents of Linux

INFO: Building Linux

<snip>

And the compilation log are stored in build.log in the $(PETALINUX)/build directory.

petalinux-package --boot --fsbl <Path to FSBL image> --fpga <Path to FPGA bitstream> --uboot=<Path to uboot image> -o <output file>

petalinux-package command requires bootgen utility to be present in $PATH. Refer Vivado tools installation section for further information

Boot.bin boot image and image.ub kernel image for Zynq get generated at

Copy following files to SD card.

This section describes about the ZC702 board setup and PetaLinux execution on 32 bit ECC proxy system

Note: After executing u-boot commands, Kernel starts booting from 32 bit Proxy memory region.

It displays Sobel Filter Demo main menu on serial utility

Exercise different options by entering the use case number displayed in the below Table against Enter your choice: on the terminal. Refer to Section 10.5: Run UART Menu Application in 1080P Mode of Zynq Base TRD wiki page to know about the available options.

Implementation

| Implementation Details | |

| Design Type | PS + PL |

| SW Type | Linux |

| CPUs | 2 ARM Cortex-A9 667MHZ |

| PS Features |

|

| Xilinx Tools Version | Vivado 2014.1 |

| Board | ZC702 Rev 1.0 |

| Files Provided | |

| ZYNQ7000AP_Soc_BaseTRDExecutionfrom32bitECCProxySystem.zip | See Appendix A for the descriptions of the files |

Prerequisites

- The ZC702 Evaluation Kit ships with the Xilinx Vivado™ Design Suite Device-locked to the Zynq-7000 XC7Z020 CLG484-1 device.

- A Linux development PC with the ARM GNU tools installed.

- A Linux development PC with the distributed version control system Git installed. For more information, refer to the Xilinx Git wiki and to UG821: Xilinx Zynq-7000 SoC Software Developers Guide.

- A Linux development PC with PetaLinux SDK installed. For more information, refer to Xilinx PetaLinux user manuals.

- Xilinx IP evaluation licenses for the Video Timing Controller and Chroma Resampler IP cores can be ordered online.

- Xylon logiCVC-ML is shipped as evaluation IP core that does not require a license. License options are listed on the Xylon logiCVC-ML product site

- Download design files (ZYNQ7000AP_Soc_32bitECCProxy.zip) from link provided above under Implementation details. Extract its content to Proxy home directory referred to as ZYNQ_TRD_PROXY_HOME in this document.

Description

Zynq Programmable Logic (PL) based reference design is developed to support 32 bit DDR access with ECC support. To provide an example design executing from 32 bit ECC protected region, Zynq base TRD is integrated along with ECC proxy system. Following are the overview about both reference designs:About Base TRD

The Base TRD is an embedded video processing application designed to showcase various features and capabilities of the Zynq Z-7020 SoC device for the embedded domain. The Base TRD consists of two elements: The Zynq-7000 SoC Processing System (PS) and a video processing pipeline implemented in Programmable Logic (PL). The SoC allows the user to implement a video processing algorithm that performs edge detection on an image (Sobel filter) either as a software program running on the Zynq-7000 SoC based PS or as a hardware accelerator inside the SoC based PLFor additional, please refer toUG925: Zynq-7000 SoC: ZC702 Base Targeted Reference Design User Guide.

About 32 bit ECC proxy system

For Zynq to support 32 bit ECC on DDR device, a solution called “ECC Proxy” has been developed which adds ECC to selected address range in DDR. ECC Proxy block adds byte level ECC to each AXI transaction. With Byte level ECC, 1 ECC byte is used for each data byte which doubles the amount of read or writes data. Transactions protected by the ECC proxy will have increased latency because effective memory bandwidth is reduced. System level performance will be less affected since the primary usage is to load DDR data to L2 cache. Outside of the increased memory latency to protected regions of DDR, the use of ECC protection should be transparent to the system.Application Processer unit (APU) of Zynq-7000 SoC normally accesses external DDR memory via L2 cache. All coherent access from APU goes through Snoop control unit (SCU) which in turn connected to L2-cache controller. There is dedicated port from L2- controller to DDR controller for reducing latency in accessing external DDR memory.

When the ECC proxy is added to the Programmable Logic (PL) as shown below, APU transactions to General purpose Master AXI interface (M_AXI_GP1) are redirected to DDR through the ECC proxy, which adds ECC protection bytes to each data bytes. Data movement to/from DDR will be through High Performance Slave (HP) port.

| Figure 1: 32 bit ECC Proxy System |

For Proxy system level details, refer to ZYNQ7000AP_SoC_ProxyDesign.pdf which is provided along with design files under ZYNQ_TRD_PROXY_HOME /doc folder. Appendix A provides details about design files.

System Overview:

To support this system, DDR memory region is divided in following region

- ECC protected region: This region is of size 368 MB. Address range is 0x8100_0000 to 0x97FF_FFFF. This region is capable of doing ECC for any kind of data/instruction transaction. It is physically mapped by proxy system to DDR address range from 0x0200_0000 to 0x3000_0000.

In this system, ECC protected region is used as a system memory. This section is used to execute Linux kernel as well as user space application. Linux kernel data and code section resides here.

- Non ECC region: It is used to do 32 bit Non ECC transactions. It is divided in two region

- Video Memory: It is of size 256 MB. Address range from 0x3000_0000 to 3xFFFF_FFFF. User can use this area for Non-ECC data of data/instruction transaction.

This memory region is used to store incoming Video data from Test pattern generator (TPG) or HDMI Input. Software Sobel filter application executing from 32 bit ECC protected region, get the video from this memory and process it. After processing, Sobel filter application store processed Video data back to this memory for Display.

- Unused Memory: It is of size 32 KB of Size. It starts from 0x0000_0000 to 0x0200_0000. User can use it for 32 bit non ECC transactions. In current implementation this memory region is unused.

Below is PS address space for above mentioned use-case

| Figure 2: PS Address Map for 32 bit ECC proxy System |

Above figure depicts M_AXI_GP1 address space from 0x8100000 to 0x97FFFFFF maps to DDR memory space starts from 0x0200_0000 to 0x2FFF_FFFF. This ECC protected region is defined with in the physical system address space with a 1MB granularity.

DDR ECC protected region addresses are expanded by 2x of M_AXI_GP1 ECC protected area. That is for each byte written through M_AXI_GP1 interface is expanded because of additional ECC byte written along with the data byte. So half of the complete ECC protected region in DDR is used for ECC protected data and half for byte level ECC storage.

Hardware Development:

Building FPGA bitstream

This section explains how to generate the FPGA hardware bitstream using the Xilinx Vivado tool (version: 2014.1) and how to export the hardware platform to Xilinx Software Development Kit (SDK) for software application development.

Steps for building the FPGA hardware bitstream

- Launch Vivado tool.

- cd $ZYNQ_TRD_PROXY_HOME/hardware/Vivado

- source ./scripts/project.tcl

| Figure 3: Vivado Tool |

The above step creates a project for Zynq 32 bit DDR proxy.

In the Flow Navigator pane on the left-hand side under Program and Debug, click Generate Bitstream. The bitstream will be generated at $ZYNQ_TRD_PROXY_HOME/hardware/vivado/project/zynq_base_trd_2013.4.runs/impl_1/ system_top_wrapper.bit

| Figure 4: Vivado IPI Block Diagram |

Exporting the Hardware Platform to SDK

A pre-generated hardware platform project can be foundat $ZYNQ_TRD_PROXY_HOME/software/workspace/hw_platform/Steps for exporting the hardware platform to SDK

From the Vivado menu bar, select File > Export > Export Hardware for SDK

| Figure 5: Exporting Hardware Platform to SDK |

In the Export Hardware for SDK window press OK. The SDK hardware platform will be exported to $ZYNQ_TRD_PROXY _HOME/hardware/vivado/project/zynq_base_trd_2013.4.sdk/SDK/SDK_Export

Note: If the Launch SDK option is checked in the Export Hardware window, SDK will be launched immediately after SDK export has completed. This is not recommended at this point.

Software Development

Building the Frist Stage Bootloader (FSBL)

This section explains how to import and build the First Stage Boot Loader (FSBL) and the standalone OS based Board Support Package (BSP) from the provided SDK projects.Precompiled zynq_fsbl.elf is provided along with design file under following directory

ZYNQ_TRD_PROXY_HOME/ready_to_use folder. If user want to use precompiled zynq_fsbl.elf, than skip this section.

Note: The provided FSBL project is a customized version of the FSBL SDK project template. The following features have been edited to support this design:

- LoadBootImage() function under image_mover.c is modified to support application download to 32 bit proxy address space. In this function partition load address range checking is disabled.

- PcapLoadParition() functionunder pcap.c is modifiedto enable level shifters and deasserting FCLK_RESET0_N reset from PS to PL logic. It is done by calling ps7_post_config() function inside PcapLoadParition() function.

- General Debug prints are enabled by defining FSBL_DEBUG under fsbl_debug.h

- ddr_clean() function is added in main.c. It is used to fill complete DDR memory space with zeros. This function is getting executed after ps7 initialization is done.

- Refer to Section 4: Building the Frist Stage Boot Loader(FSBL) of Zynq Base TRD wiki Link to get more details about other FSBL changes required for TRD execution.

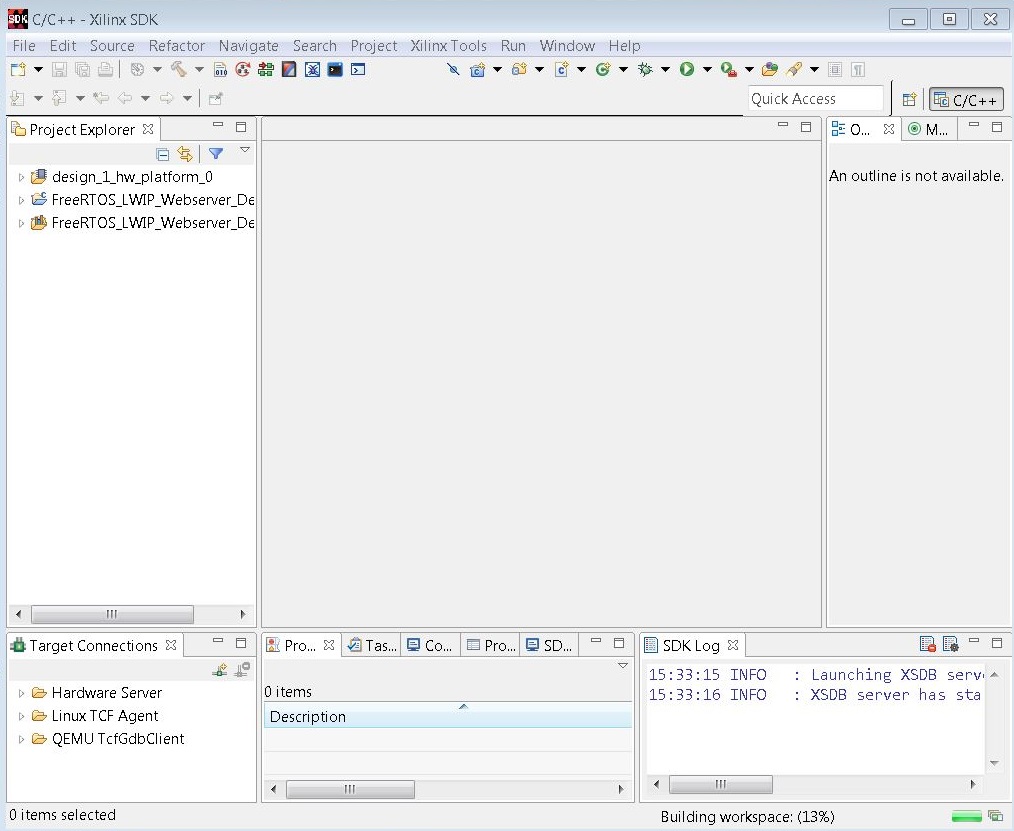

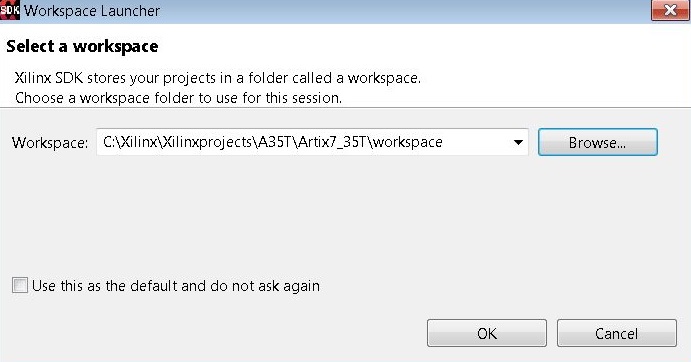

- Launch SDK tool.

- In the Workspace Launcher window, click Browse and navigate to $ZYNQ_TRD_PROXY_HOME/software/workspace, then click OK. Close the welcome screen.

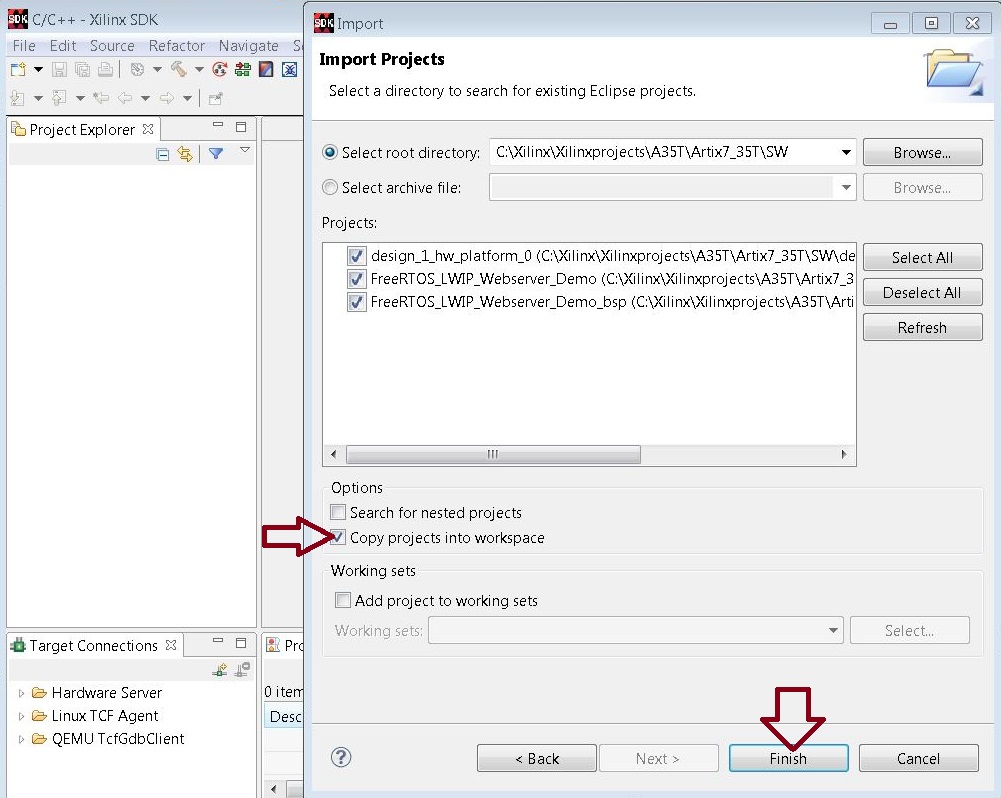

- Select File > Import, to import the hardware platform (hw_platform) , FSBL (zynq_fsbl) and FSBL BSP (zynq_fsbl_bsp) into the SDK workspace. It opens Import wizard

Figure 6: import wizard - In the Import wizard, expand the General folder, select Existing Projects into Workspace, and click Next.

figure 7: import wizard - Select “Select archive file” option and Click Browse to navigate to $ZYNQ_PROXY_HOME/software/workspace/workspace.zip.

- Press Finish.

| Figure 8: Import Wizard |

The build process will start automatically and builds the BSP first and then the FSBL. The generated Zynq FSBL executable can be found at $ZYNQ_TRD_PROXY_HOME/software/workspace/zynq_fsbl/Debug/zynq_fsbl.elf

Porting and building the PetaLinux

Installation of PetaLinux SDK

Prerequisites

- 2GB RAM (recommended minimum for Xilinx tools)

- Pentium 4 2GHz CPU clock or equivalent.

- 5 GB free HDD space.

- 4.Supported OS:

- RHEL 5 (32-bit or 64-bit)

- RHEL 6 (32-bit or 64-bit)

- SUSE Enterprise 11 (32-bit or 64-bit)

- PetaLinux release package downloaded.

- Valid PetaLinux license.

- Common system packages and libraries are installed on your workstation. The installation process will check for these. See the section Required Tools and Libraries for more details. For detailed information refer PetaLinux installation guideUG976 .

Extract the PetaLinux Package

Assuming all the prerequisites described in the last subsection are satisfied, PetaLinux installation is very straight forward. Without any options, the installers will install as a subdirectory of the current directory. Alternatively, an installation path may be specific. Run the downloaded PetaLinux installer.bash> ./petalinux-v2013.10-final-installer.run

PetaLinux will be installed in the petalinux-v2013.10-final directory, directly underneath the working directory of this command.

So, if you install the installer into your home directory /home/user, PetaLinux will be installed in /home/user/petalinux-v2013.10-final.

You may move the resulting petalinux-v2013.10-final directory to a preferred location before continuing.

Install License

PetaLinux licenses are managed using the same system as all other Xilinx Design Tools. For more details on licensing and setup of license please refer to the"Xilinx Design Tools: Installation and Licensing Guide (UG798)" section "Obtaining and Managing a License".

Setup PetaLinux Working Environment

After extracting the package, the remainder of the setup is completed automatically.- Go to the PetaLinux root directory by running this command on the command console:

e.g.:

bash> cd /home/user/petalinux-v2013.10-final

- Source the appropriate PetaLinux setup script by running this command on the command console:

bash> source settings.sh

The first time the setup script is sourced, it will perform some post installation tasks to check system dependencies and initialize the Linux kernel source tree.Below is an example of the output from sourcing the setup script for the first time:

PetaLinux environment set to ’/home/user/petalinux-v2013.10-final

INFO: Finalizing PetaLinux installation

INFO: Checking free disk space

INFO: Checking installed tools

INFO: Checking installed development libraries

INFO: Checking network and other services

The post-install step only occurs once. Subsequent runs of the settings script should be much quicker, and simply output a confirmation message such as that shown below:

PetaLinux environment set to ’/home/user/petalinux-v2013.10-final'

Verify PetaLinux Installation

Verify that the PetaLinux working environment has been set:bash> echo $PETALINUX

/home/user/petalinux-v2013.10-final

Environment variable "$PETALINUX" should point to the path to the installed PetaLinux. Your echo output may be different from this example, depending upon where you installed PetaLinux.

PetaLinux Porting

ZC702 Board support Package (BSP) installation

PetaLinux includes reference designs for you to start working with and customize for your own projects. These are provided in the form of installable BSP (Board Support Package) files, and include all necessary design and configuration files, including pre-built and tested hardware and software images, ready for download to your board or for booting in the QEMU system simulation environment.

Run petalinux-create command on the command console:

petalinux-create -t project -s <path-to-bsp>

bash> cd $PETALINUX bash> petalinux-create -t project -s /$ZYNQ_TRD_PROXY_HOME/software/petalinux/bsp/Xilinx-ZC702-trd-v2013.4.bsp

INFO: Projects:

INFO: * zynq_base_trd_2013.4

<snip>

Linux Kernel and u-boot configuration

Zynq Base TRD uses Xilinx Linux 3.12 kernel version. PetaLinux provides option to add individual project specific kernel/u-boot version. Below steps demonstrates how to add/config/build the Linux kernel.- Follow following steps to download Xilinx Linux 3.12 Kernel version from GIT repository.

bash> cd $PETALINUX/zynq_base_trd_2013.4/components bash> mkdir linux-kernel bash> cd linux-kernel bash> git clone git://github.com/Xilinx/linux-xlnx.git bash cd linux-xlnx

Bash> git checkout -b zynq_base_trd_v2013.4 xilinx-v2013.4-trd

- Apply the Base TRD specific patch on top of the xilinx-v14.7. The patch includes:

- Mouse sensitivity patch (As default mouse sensitivity on embedded QT GUI is quite fast)

bash> cp $ZYNQ_TRD_PROXY_HOME/software/patch/zynq_base_trd_v2013_4.patch . //Copy 2013.4 TRD patch to kernel dir bash> git apply --stat zynq_base_trd_v2013_4.patch // display contents of patch bash> git apply --check zynq_base_trd_v2013_4.patch // check if patch can be applied bash> git am zynq_base_trd_v2013_4.patch // apply the patch

- PetaLinux configuration help us to select custom kernel required for Zynq Base TRD project

bash> petalinux-config

| Figure 9: Linux Configuration Wizard |

Select kernel menu in Linux configuration. It opens Kernel selection sub-menu.

| Figure 10: Kernel Selection |

Select linux-xlnx kernel. Press Enter.

- Do following Linux kernel configuration modification for Zynq 32 bit ECC proxy

| Figure 11: Linux Configuration Wizard |

Select Kernel Base address in Linux Configuration. It opens Kernel base address sub menu

| Figure 12: Kernel Base Address Wizard |

- Change Kernel Base address from 0x0 to 0x81000000 and Select OK.

- Select Exit from Linux Configuration

- Select Yes for “Do you wish to save your new configuration?”

- Open xparameters.h

bash> vi $PETALINUX/zynq_base_trd_2013.4/subsystems/linux/hw-description/xparameters.h**

Change following definition and save the file.i

- #define XILINX_RAM_START 0x81000000

- #define XILINX_RAM_SIZE 0x17000000

- Replace $PETALINUX/ zynq_base_trd_2013.4/subsystems/linux/hw-description/system.dts with $ZYNQ_TRD_PROXY_HOME/software/system.dtsfile.

- Open zynq-zc702.dts

bash> vi $PETALINUX/ zynq_base_trd_2013.4/subsystems/linux/hw-description/zynq-zc702.dts

memory {

device_type = “memory”;

reg = <0x81000000 0x17000000>;

}

- Open Config.mk

bash>vi $PETALINUX/ zynq_base_trd_2013.4/subsystems/linux/hw-description/Config.mk

- TEXT_BASE= 0x9f000000

- CONFIG_SYS_TEXT_BASE= 0x9f000000

Building PetaLinux

Run ’petalinux-build’ in the PetaLinux SDK project directory to build the PetaLinux system image

bash> cd $PETALINUX/zynq_base_trd_2013.4 bash> petalinux-build

The console shows the compilation progress. e.g.:

INFO: Checking component...

INFO: Generating make files and build Linux

INFO: Generating make files for the subcomponents of Linux

INFO: Building Linux

<snip>

And the compilation log are stored in build.log in the $(PETALINUX)/build directory.

Generate BOOT image for Zynq

Follow the steps below to generate the SD boot image (BOOT.BIN).petalinux-package --boot --fsbl <Path to FSBL image> --fpga <Path to FPGA bitstream> --uboot=<Path to uboot image> -o <output file>

petalinux-package command requires bootgen utility to be present in $PATH. Refer Vivado tools installation section for further information

bash> cd $PETALINUX/ zynq_base_trd_2013.4/images/linux bash> petalinux-package --boot --fsbl $ZYNQ_PROXY_HOME/software/workspace/zynq_fsbl/Debug/zynq_fsbl.elf --fpga $ZYNQ_PROXY_HOME/hardware/vivado/project/zynq_base_trd_2013.4.runs/impl_1/system_top_wrapper.bit --uboot

bash> cd $PETALINUX/Xilinx-ZC702-2013.3/images/linux

Copy following files to SD card.

- BOOT.bin

- Image.ub.

- Autostart.sh ($ZYNQ_TRD_PROXY_HOME/ready_to_test)

ZC702 Board Setup:

This section describes about the ZC702 board setup and PetaLinux execution on 32 bit ECC proxy system

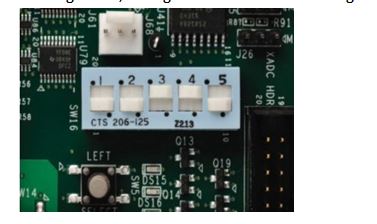

- Make sure that the hardware board is set up is done properly.Note:Refer to Section 10.2 Board setup of Zynq Base TRD wiki page

- For SD card booting mode, Change the SW16 switch setting as shown below

| Figure 13: Switch setting for SD boot mode |

Video Application Execution

Follow the following procedure for Application execution- Make sure that the hardware board is set up is done properly as discussed in above section.

- Insert a SD-MMC memory card, which contains BOOT.bin , image.ub and autostart.sh into the SD slot on the ZC702 board

- Switch ON ZC702 board.Note: By doing so FSBL start executing and download u-boot at defined location. After downloading it handoff execution to u-boot.Prints get display on the serial console.

- During u-boot execution, the auto boot countdown message appears on serial consol. Hit any key to stop autoboot: 4

- Press Enter on serial console.Automatic booting from U-Boot stops and au-boot-PetaLinux>prompt appears on the serial terminal.

- On serial console u-boot-PetaLinux> prompt do following commands,

u-boot-PetaLinux> setenv fdt_high 0x90000000 u-boot-PetaLinux> saveenv u-boot-PetaLinux> fatload mmc 0 0x93000000 image.ub U-boot-PetaLinux> bootm 0x93000000

Note: After executing u-boot commands, Kernel starts booting from 32 bit Proxy memory region.

- Waits for Kernel to boot. Provide login and password as (root/root). Once Kernel boots,**root@Xilinx-ZC702-2013_4~#**prompts appears on serial console.

- To check memory map, type following commands

root@Xilinx-ZC702-2013.3~# cat /proc/iomem

- It shows following memory map.

00000008-0002ffff : f800c000.ps7-ocmc 40090000-4009ffff : /amba@0/axivdma@0x40090000 400b0000-400bffff : /amba@0/axivdma@0x400B0000 81000000-97ffffff : System RAM 81008000-815a71fb : Kernel code 873a8000-87415427 : Kernel data e0001000-e0001ffe : xuartps e0002000-e0002fff : /amba@0/ps7-usb@e0002000 e0002000-e0002fff : /amba@0/ps7-usb@e0002000 e0004000-e0004fff : /amba@0/ps7-i2c@e0004000 e000a000-e000afff : /amba@0/ps7-gpio@e000a000 e000b000-e000bfff : /amba@0/ps7-ethernet@e000b000 e000d000-e000dfff : /amba@0/ps7-qspi@e000d000 e0100000-e0100fff : mmc0 f8003000-f8003fff : /amba@0/ps7-dma@f8003000 f8003000-f8003fff : /amba@0/ps7-dma@f8003000 f8005000-f8005fff : /amba@0/ps7-wdt@f8005000 f8007000-f80070ff : /amba@0/ps7-dev-cfg@f8007000f8007100-f800711f : /amba@0/ps7-xadc@f8007100 f800c000-f800cfff : /amba@0/ps7-ocmc@f800c000 ffff0000-ffffffff : f800c000.ps7-ocmc

- Kernel code section mapped from 0x81008000 to 0x815a71fb.

- Kernel data section mapped from 0x873a8000to 0x873a8000.

- System Memory mapped from 0x81000000 to 0x97ffffff.

- Type Following command to execute Sobel Filtering Application for HD resolution display (1080P) from 32 bit ECC protected area.

root@Xilinx-ZC702-2013.3~# run_sobel.sh -cmd -res 1920x1080

It displays Sobel Filter Demo main menu on serial utility

| Figure 14: Sobel Filter Demo Main Menu |

Exercise different options by entering the use case number displayed in the below Table against Enter your choice: on the terminal. Refer to Section 10.5: Run UART Menu Application in 1080P Mode of Zynq Base TRD wiki page to know about the available options.

Appendix A: File Descriptions in the design directory

Directory Structure is- ZYNQ_TRD_PROXY_HOME

- doc:

- ZYNQ7000AP_SoC_ProxyDesign.pdf: It provides detail about 32 bit ECC proxy system.

- hardware:

- Vivado:

- constrs: It contains “system_top.xdc” constraint file for the design.

- scripts: It contains following TCL files to create project and system block diagram.

- project.tcl: Script file to create ZC702 project in Vivado.

- build_bd_design.tcl: Script file to create system block diagram. It get execute from protect.tcl file.

- Impl_batch.tcl: script file to do implementation.

- srcs:

- ip: It contains IPs used in the design.

- hdl: Top level Verilog file for design.

- Vivado:

- software:

- workspace: It contains archive project file for SDK.

- petalinux: It contains board support package (BSP) files used by petaLinux to generateTRDBSP for ZC702 board.

- system.dts: TRD based system device tree file.

- ready_to_test

- BOOT.bin: Booting image.

- Image.ub: Kernel image.

- autostart.sh: Script file to run Sobel filer application

- doc:

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy