Xilinx V4L2 DisplayPort 1.4 RX Subsystem Driver

The purpose of this page is to describe the Linux V4L2 driver for the Xilinx DisplayPort 1.4 RX Subsystem Soft IP for Zynq UltraScale+ MPSoC and for Versal.

Note: The content of this page is applicable for the 2022.1 release. A few steps for building the kernel or taking sources from Git might be different for previous releases before 2022.1.

Table of Contents

Introduction

The DisplayPort (DP) 1.4 Receiver Subsystem is a plug-in solution for serial digital video data reception in large Video systems of up to video resolutions of Full Ultra HD (FUHD) at 30 fps.

It has the dynamic support of BPC (Bits per pixel) and different color formats. DisplayPort ( DP) 1.4 core supports 4 data lanes and each lane supports dynamic data rate up to 8.1Gb/s. It is a feature-rich soft IP incorporating all the necessary logic to properly interface with PHY layers and provide DP decoding functionality. The subsystem is a hierarchical IP that bundles a collection of DP RX-related IP sub-cores and outputs them as a single IP. The subsystem outputs multi-pixel video to AXI4-Stream Protocol interface. Below is the block diagram of the DisplayPort 1.4 Rx Subsystem.

Figure 1. Block diagram of the DisplayPort 1.4 Rx subsystem

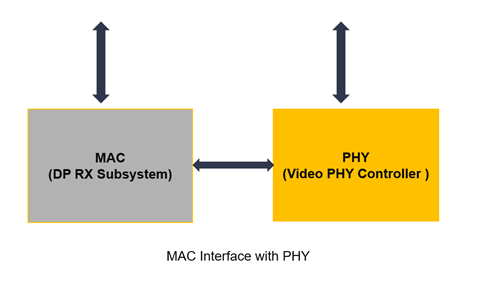

DP Rx interface with Video PHY Controller for Zynq UltraScale+ MPSoC

Figure 2. Block diagram of MAC interface with PHY for Zynq

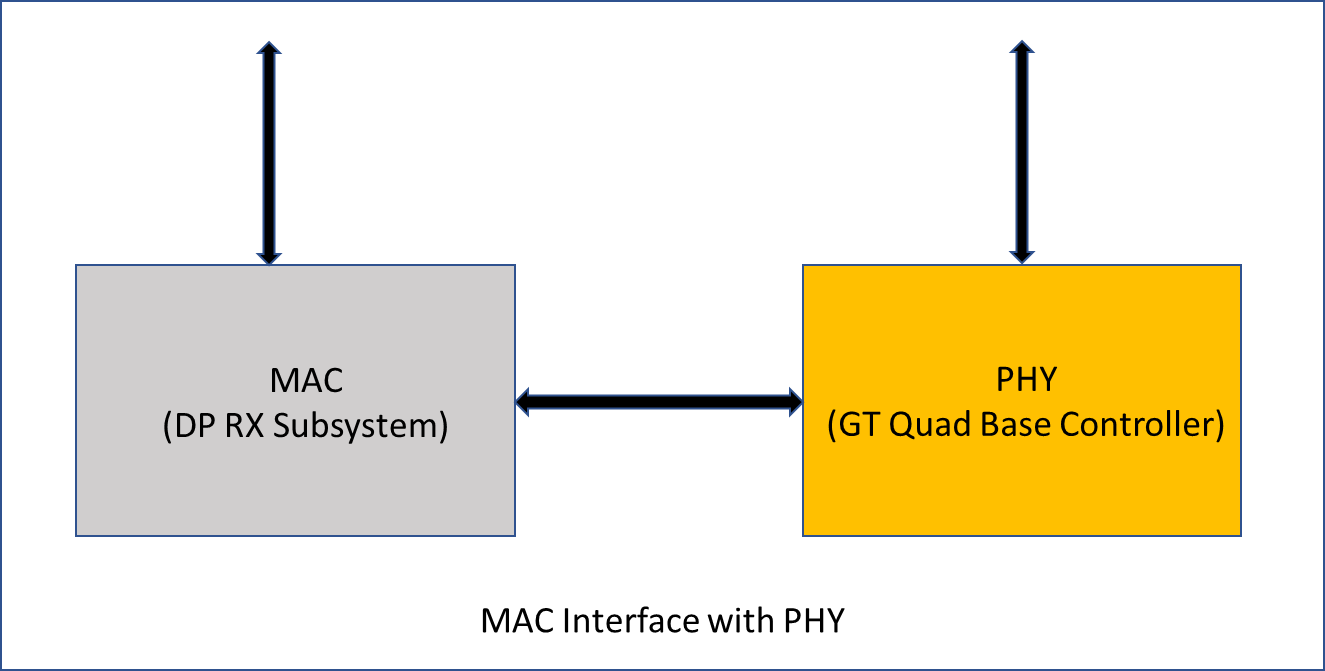

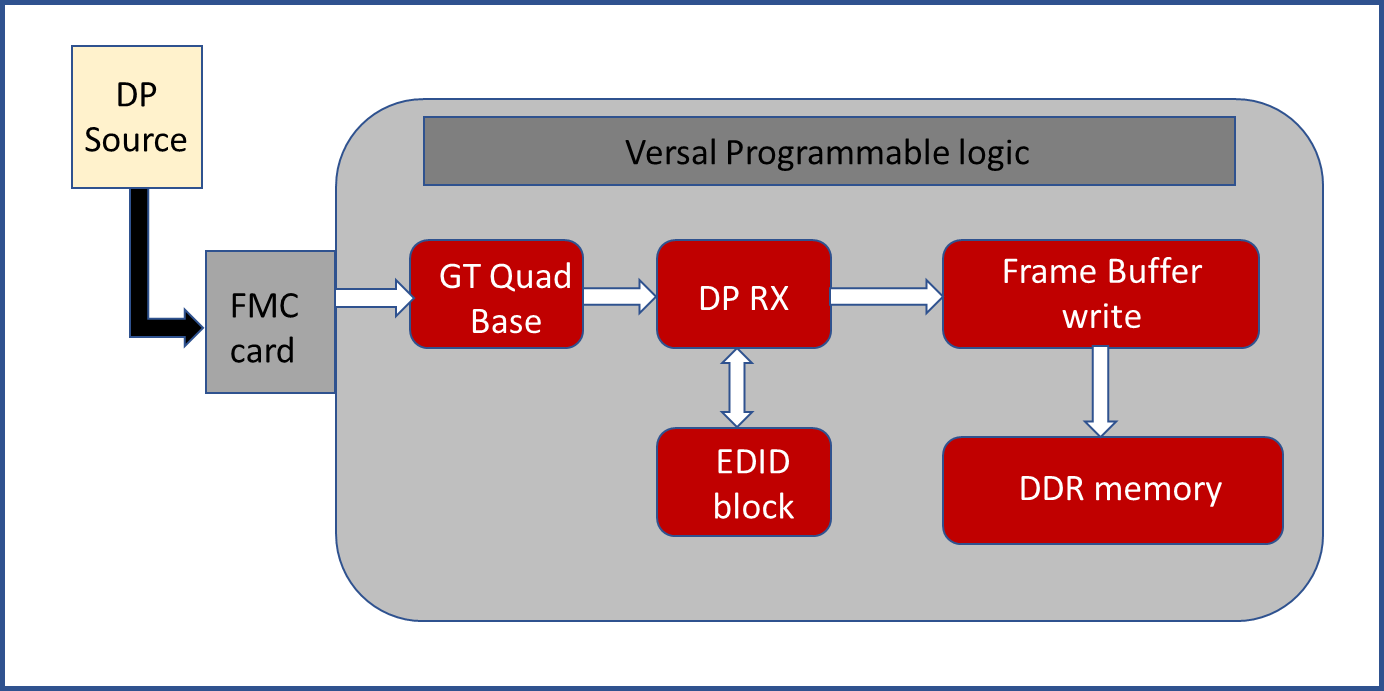

DP Rx interface with GT Quad base Controller for Versal

The DP 1.4 Receiver Subsystem is a MAC subsystem which works with a GT Quad Base Controller (PHY) to create a video connectivity system. The DP 1.4 Receiver Subsystem is tightly coupled with the Xilinx PHY Controller, which itself is independent and offers flexible architecture with multiple-protocol support. Both the MAC and PHY are dynamically programmable through the AXI4-Lite interface.

Figure 3. Block diagram of MAC interface with PHY for Versal

Driver Overview

DP Rx is the first node in the capture pipeline. The Linux driver is implemented within the V4L2 framework and creates a subdev node ( /dev/v4l2-subdev* ) which can be used to query the DP IP core. The DP Rx driver provides an abstracted view of the feature set provided by each included sub-core. It dynamically manages the data and control flow through the processing elements, based on the input stream configuration detected at run time. The general description of V4L2 framework is documented here: v4l2-framework.txt.

The Xilinx DP Rx is tightly coupled with the Xilinx video PHY driver and manages the interaction with the PHY layer internally. The Xilinx VPhy driver is an integral part of the solution and is automatically pulled-in when Xilinx DP Rx driver is selected in the kernel configuration.

For Versal, The PHY (GT Quad Base) driver need to be selected in kernel configuration.

MCDP6000 Retimer driver callback implementation:

The Xilinx solution expects the use of the MCDP6000 Retimer along with the DisplayPort 1.4 RX Subsystem solution. MCDP6000 as a retimer provides better SI features. As a retimer, the MCDP6000 removes the random and ISI jitter from the video source. For the Xilinx DisplayPort, MCDP6000 configuration is controlled through an I2C interface. For a DisplayPort 1.4 solution, the MCDP6000 retimer chip is present on the FMC card and the driver for this chip is developed as a part of FMC driver.

Because the DisplayPort 1.4 Rx driver handles the required MCDP6000 configurations, DP 1.4 Rx driver needs register the callback functions of the FMC driver. These functions will be called from the DP 1.4 Rx Driver interrupt context. Below are driver and device tree changes to achieve this callback mechanism.

- Add reference to the FMC node in the DP 1.4 RX Device tree node. Below is an example.

dp_rx_hier_0_v_dp_rxss1_0: v_dp_rxss1@a0040000 {

clock-names = "s_axi_aclk", "rx_vid_clk", "m_axis_aclk_stream1", "rx_lnk_clk", "m_aud_axis_aclk";

clocks = <&zynqmp_clk 71>, <&zynqmp_clk 72>, <&zynqmp_clk 72>, <&misc_clk_1>, <&zynqmp_clk 71>;

compatible = "xlnx,v-dp-rxss-3.0","xlnx,vid-edid-1.0";

interrupt-names = "dprxss_dp_irq";

interrupt-parent = <&gic>;

interrupts = <0 89 4>;

reg = <0x0 0xa0040000 0x0 0x40000>,<0x0 0xa0010000 0x0 0x10000>;

reg-names = "dp_base", "edid_base";

xlnx,dp-retimer = <&xfmc>;

-----------

-----------

------------

};

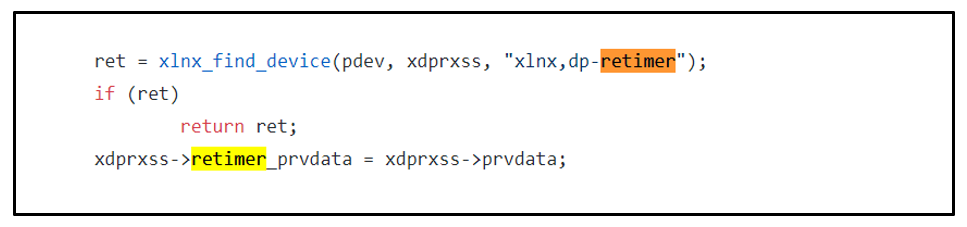

- Implement Retimer configuration structure in the DP 1.4 Rx driver

- Assign the FMC driver private data pointer to the DP 1.4 Rx driver member pointer

- The DP 1.4 Rx drive will use the xdprxss→retimer_prvdata pointer to call the FMC driver callbacks. For more information, see DP 1.4 Rx Linux driver.

Driver Features

| IP Feature | 2020.2 | 2021.1 | 2021.2 | 2022.1 | 2022.2 | 2023.1 | 2023.2 | 2024.1 |

| IP version | 3.0 | 3.0 | 3.0 | 3.0 | 3.1 | 3.1 | 3.1 | 3.1 |

| eDP and iDP supported. | No | No | No | No | No | No | No | No |

Supports AXI4-Stream, native video input interfaces | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Support for 2 pixels per sample | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Support color space for RGB, YUV 4:4:4, YUV 4:2:2 | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Support AXI4-Stream Video output stream and Native Video output stream | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only |

| Support for 2 channel audio with 44/48 KHz sample rates. | No | No | No | Yes | Yes | Yes | Yes | Yes |

| 8, 10, 12, or 16 bit per color component | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only | Supports 8,10 bpc only |

| Support for 16-bit GT width. | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| Support for HDCP in MST mode | No | No | No | No | No | No | No | No |

| Supported resolution up to 8k30 | Yes | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| 420 Colorimetry | No | No | No | No | No | No | Yes | Yes |

| Support for interlaced video in AXI4-Stream Interface | No | No | No | No | No | Yes | Yes | Yes |

| Dual-pixel splitter in native video mode | No | No | No | No | No | No | No | No |

| Supports SDP packet for static HDR mode | No | No | No | No | Yes | Yes | Yes | Yes |

| Supports HDCP 1.3 and HDCP 2.2 decryption in SST | No | No | No | No | Supports only HDCP 1x | Supports only HDCP 1x | Supports HDCP 1x and HDCP 2x | Supports HDCP 1x and HDCP 2x |

| Versal Support | No | No | No | Yes | Yes | Yes | Yes | Yes |

| GTHE4 Support | No | Yes | Yes | Yes | Yes | Yes | Yes | Yes |

| GTYE5 Support | No | No | No | Yes | Yes | Yes | Yes | Yes |

Missing Features / Known Issues / Limitations in Driver

- This driver does not support the following features.

- MST

- GTYE4

Kernel Configuration Options for Driver

- Enable Xilinx DP Rx Subsystem driver

2021.1 and onwards: the DisplayPort Rx driver is built as a part of the kernel, so enable the DisplayPort Rx driver in the kernel configuration. Run the below command from the PetaLinux project and select "Xilinx DP Rx Subsystem".

$petalinux-config -c kernel

- Enable Video PHY and FMC drivers

- 2021.1 and onwards FMC driver is built as out-of-tree kernel module and therefore requires no kernel configuration. However, to enable the driver, the user must include it in the rootfs.

- 2021.2 and onwards The Video phy controller driver is built as out-of-tree kernel module and therefore requires no kernel configuration. However to enable the driver, the user must include it in the rootfs. The following steps are required to enable the driver.

- Make sure that the meta-user layer has the recipe-dp included.

Add the recipe to the PetaLinux image. Edit project-spec/meta-user/conf/user-rootfsconfig and add the new recipe at the end:

CONFIG_kernel-module-dp

Next include the driver in the rootfs

$petalinux-config -c rootfs

Select "user-pakages->modules->kernel-module-dp", save and exit

- Enable the GT QUAD base driver

2022.1, the video phy driver for Versal systems is built as part of kernel., so enable this driver in the kernel configuration. Run the below command from the PetaLinux project and select "PHY_XILINX_DPGTQUAD".

$petalinux-config -c kernel

- Enable Audio drivers

2022.1, the DP Rx driver supports audio and works with ALSA framework, Run the below command from the PetaLinux project and select "CONFIG_SND_SOC".

$petalinux-config -c kernel

Build the project

$petalinux-build

Device Tree Binding

The dts node should be defined with correct hardware configuration. An example device tree node is documented in

- 2020.1 : dp-modules/Documentation/devicetree/bindings/xlnx,v-dp-rx-ss.txt - Deprecated

2020.2 : https://github.com/XilinxDocumentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml - Deprecated

2021.1 : Documentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml - Deprecated

2021.2 : Documentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml - Deprecated

2022.1 : Documentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml

2023.2 : Documentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml

2024.1 : Documentation/devicetree/bindings/media/xilinx/xlnx,v-dprxss.yaml

Building Driver Modules in OSL flow

Note: The below steps are applicable for building images for 2020.1. These steps are deprecated. Customers are advised to use 2022.1 onwards drivers and the device tree.

- Create a directory to build driver modules in local machine.

- example : mkdir build_dir

- clone the linux-xlnx from git https://github.com/Xilinx/linux-xlnx.git to build_dir.

- cd build_dir

- git clone https://github.com/Xilinx/linux-xlnx.git

- Clone the dp-modules to build_dir directory

- git clone https://github.com/Xilinx/dp-modules.git

- create a directory for the kernel output

- mkdir kernel_output

Create a make file and copy the below contents to it

export TOP_DIR = $(shell pwd)

BOARD_NAME := zcu102

export ARCH = arm64

GCC_PREFIX = <cross-compiler path>

export DP_SOURCE := $(TOP_DIR)/dp-modules

export KERNEL_SOURCE := $(TOP_DIR)/linux-xlnx

export OUTPUT_DIR := $(TOP_DIR)/kernel_output

export KERNEL_OUTPUT := $(OUTPUT_DIR)/linux-xlnx-$(ARCH)

kernel:

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -C $(KERNEL_SOURCE) xilinx_zynqmp_defconfig O=$(KERNEL_OUTPUT)

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) O=$(KERNEL_OUTPUT) Image

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) O=$(KERNEL_OUTPUT) modules

modules:

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) M=$(DP_SOURCE) O=$(KERNEL_OUTPUT) modules

find $(DP_SOURCE) -type f -name '*.o' -delete

find $(DP_SOURCE) -type f -name '*.cmd' -delete

find $(DP_SOURCE) -type f -name 'Modules' -delete

find $(DP_SOURCE) -type f -name 'Module.*' -delete

find $(DP_SOURCE) -type f -name '*.order' -delete

find $(DP_SOURCE) -type f -name '*.mod.c' -delete

find $(DP_SOURCE) -type f -name '*.mod' -delete

run the below command to build the kernel

- $ make kernel

- run the below command to build the dp-modules

- $make modules

- Now the DP Rx driver is ready to use.

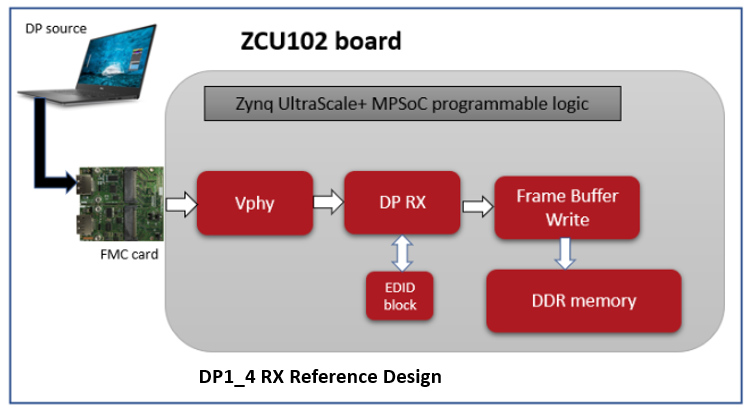

Reference Design for Zynq UltraScale+ MPSoC:

Figure 4. DisplayPort Rx example design architecture

Reference Design for Versal

Figure 5. DisplayPort Rx example design architecture for Versal

Test Procedure

Test procedure for video capture and play

The driver has been tested using the YAVTA tool and GStreamer framework.

On cable connect, the Rx core will detect the input stream and set the MEDIA_BUS format accordingly. Video data received from Rx core is saved to DDR using framebuffer write DMA. You can query the detected format by using media-ctl utility.

root@xilinx-zcu102-2021_1:/media# media-ctl -p

Media controller API version 5.10.0

Media device information

------------------------

driver xilinx-video

model Xilinx Video Composite Device

serial

bus info

hw revision 0x0

driver version 5.10.0

Device topology

- entity 1: vcap_dp output 0 (1 pad, 1 link)

type Node subtype V4L flags 0

device node name /dev/video0

pad0: Sink

<- "a0040000.v_dp_rxss1":0 [ENABLED]

- entity 5: a0040000.v_dp_rxss1 (1 pad, 1 link)

type V4L2 subdev subtype Unknown flags 0

device node name /dev/v4l-subdev0

pad0: Source

[fmt:RBG888_1X24/3840x2160 field:none colorspace:rec709]

[dv.caps:BT.656/1120 min:800x600@25000000 max:7680x4320@297000000 stds:CEA-861,DMT,CVT,GTF caps:interlaced,progressive,reduced-blanking,custom]

[dv.detect:BT.656/1120 3840x2160p60 (4400x2250) stds:CEA-861 flags:can-reduce-fps,CE-video,has-cea861-vic]

-> "vcap_dp output 0":0 [ENABLED]

root@xilinx-zcu102-2022_1:/media#

Using VIDIOC_SUBDEV_G_FMT ioctl, the width, height ,format and field type (interlaced or progressive) can be determined.

The resolution info can be sent across to a video capture application such as YAVTA to capture the stream frames into the DDR using a simple design

DP-Rx SS ==>Framebuffer Write ==> Memory

For example, below is the command to capture a 1920x1080 stream using the yavta application .

yavta -n 3 -c10 -f RGB24 -s 1920x1080 --skip 9 -F /dev/video0

The captured .bin files can then be viewed in the yuvplayer.exe application.

Below is the command to capture a 1920x1080 stream using a GStreamer application .

gst-launch-1.0 v4l2src device=/dev/video0 num-buffers=2 ! video/x-raw,width=1920,height=1080,format=RGB ! filesink location=frame.rgb

The above command captures 2 frames from the input stream and saves it in a file called frame.rgb which can then be viewed in the yuvplayer.exe application.

Test procedure for Audio

The audio has been tested with ALSA utils.

Record: Records the audio data into a file.

arecord -Dhw:0,1 -fS24_LE -r 48000 -c 2 -d 30 -t raw <output filename.raw>

Device enumeration:

arecord --device="hw:0,1" --dump-hw-params

Debug Capabilities

The driver debug messages can be enabled by adding "#define DEBUG" at the top of the file.

All debug prints are sent to serial console and can be viewed in the kernel dmesg buffer.

Some tips to help debug are below:

- The DP-Rx source should be connected to DP Rx port of the FMC card and should be running.

- The driver should have been loaded successfully

Running media-ctl should show resolution and color format.

E.g. “media-ctl –d /dev/media0 –p”

Boards Supported

The driver has been tested on the following boards

- ZCU102 Rev 1.0

- VCK190

Change Log

- 2024.1

- 2023.2

- Summary:

- a89e660 v4l2: xilinx: dprx: Add HDCP2x support

- 022d9d3 v4l: xilinx: dprx: Remove 0x200 obsolete register usage

- 3733d2a v4l: xilinx: Add interface type parameter to HDCP initialize function

- 42f7575 v4l2: xilinx: dprx: Add support for YUV 420 8bpc and 10bpc color format

- 4a511ba v4l: xilinx: dprx: Correct the XDPRX_HPD_INTR_MASK macro bit mask value

- 650d180 v4l: xilinx: dprx: Add check for status1 in irq_handler

- 5ad0c90 v4l2: xilinx: dprx: Move the interrupt handlers to workqueue

- Summary:

- 2023.1

- 2022.2

- 2022.1

- Summary:

- f2e88a581130 v4l: xilinx: dprxss: Add support for Versal

- 9b62852ec04b Merge tag 'v5.15' into master

- 986aca58b142 v4l: xilinx: dprx: Disable unplug interrupt when RX is disconnected

- f6d1241bb3c4 v4l: xilinx: dprx: Fix typo in macro

- a83d69b2d8e2 v4l: xilinx: dprx: Generate HPD interrupt in unplug handler

- 535e3c204208 v4l: xilinx: dprx: Disable audio when training is lost

- 7e01e94bf687 v4l: xilinx: dprx: Correct the DTG disable sequence

- f0462a9ebeae v4l: xilinx: dprx: Update max linkrate to extended capability registers

- 1241f0ac2c23 v4l: xilinx: dprx: Set default CDR timeout value

- 8ebfdae0ac5e v4l: xilinx: dprx: Enable training timeout

- caf59ff90799 v4l: xilinx: dprxss: Add changes to get gt_quad_base as phy handle

- 5f68e6129b68 v4l: xilinx: dprx: Align kernel-doc description

- 94c6af3e9c95 v4l: xilinx: dprx: Call retimer reset functions

- 40653103453e v4l: xilinx: dprx: Reset the retimer dp data path

- be37b4278bb3 v4l: xilinx: dprx: Fix TP2 macro

- d534ae1bf76f v4l: xilinx: dprx: Implement access laneset and tp2 interrupt handlers

- 647c103aaa52 v4l: xilinx: dprx: Implement prbs7 mode enable in retimer

- 9f2b813b6fc2 v4l: xilinx: dprx: Implement prbs7 mode enable in video phy

- 96feaf25679d v4l: xilinx: dprx: Enable training related interrupts in unplug handler

- f63eb4c6a2fd v4l: xilinx: dprx: Enable audio interrupts in no video handler

- 001e0c6bf4f9 v4l: xilinx: dprx: Enable or disable INTERRUPT_CAUSE_1 interrupts

- 70f52b12363f v4l: xilinx: dprx: Add support for 8k 25fps resolution

- 5ff7cd8defe1 v4l: xilinx: dprx: Update video timings information

- 50fc7aacbe25 v4l: xilinx: dprx: Add MMCM configuration for rx_dec_clk for versal systems

- 7628155 v4l: xilinx: dprx: Add unplug handler function in work queue

- Summary:

- 2021.2

- Summary:

- 9d3bae6d6871 v4l: xilinx: Added support for DP audio

- 7a1899cdc9db v4l: xilinx: dprxss: Remove double which word

- Summary:

Related Links

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy