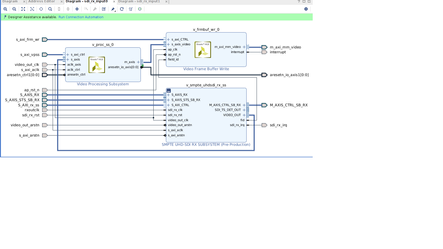

DTG limitation for multimedia IPs

There are some cases where DTG cannot generate the input and output port information for the video pipelines as there is no information from the design/hdf. For those IP's user need to update port's information inside the video pipeline IP nodes.

Here we are explaining where to add the port information for the below example cases.

Case1) For example in the design have two similar video pipelines like hdmi_rx → scaler → frmbuf_wr

The nodes for these IPs and their input and output ports are as below and this will be generated by the DTG.

1)Hdmi_rx IP

hdmi_input_v_hdmi_rx_ss_0: v_hdmi_rx_ss@a0000000 {

compatible = "xlnx,v-hdmi-rx-ss-3.1", "xlnx,v-hdmi-rx-ss-3.1";

hdmirx_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

hdmirx_port: port@0 {

/* Fill the fields xlnx,video-format and xlnx,video-width based on user requirement */

reg = <0>;

xlnx,video-format = <0>;

xlnx,video-width = <10>;

hdmi_rx_out: endpoint {

remote-endpoint = <&vpss_scaler_in>;

};

};

};

};

2) Scaler IP

hdmi_input_v_proc_ss_0: v_proc_ss@a0080000 {

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

vpss_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

vpss_port0: port@0 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <0>;

xlnx,video-format = <12>;

xlnx,video-width = <8>;

vpss_scaler_in: endpoint {

remote-endpoint = <&hdmi_rx_out>;

};

};

vpss_port1: port@1 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <1>;

xlnx,video-format = <12>;

xlnx,video-width = <8>;

vpss_scaler_out: endpoint {

remote-endpoint = <&vcap_hdmi_in>;

};

};

};

};

3) Frambuf_wr IP

hdmi_input_1_v_frmbuf_wr_0: v_frmbuf_wr@a0070000 {

#dma-cells = <1>;

clock-names = "ap_clk";

clocks = <&misc_clk_0>;

compatible = "xlnx,v-frmbuf-wr-2.1", "xlnx,axi-frmbuf-wr-v2.1";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 89 4>;

reg = <0x0 0xa0070000 0x0 0x10000>;

reset-gpios = <&gpio 93 1>;

};

vcap_hdmi {

compatible = "xlnx,video";

dma-names = "port0";

dmas = <&hdmi_input_1_v_frmbuf_wr_0 0>;

vcap_hdmi_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

vcap_hdmi_port: port@0 {

direction = "input";

reg = <0>;

vcap_hdmi_in: endpoint {

remote-endpoint = <&vpss_scaler_out>;

};

};

};

};

For the second pipeline DTG wont be generated the input and output port information and the nodes will be as below

hdmi_input_1_v_hdmi_rx_ss_0: v_hdmi_rx_ss@a0020000 {

compatible = "xlnx,v-hdmi-rx-ss-3.1", "xlnx,v-hdmi-rx-ss-3.1";

};

hdmi_input_1_v_proc_ss_0: v_proc_ss@a0200000 {

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

};

hdmi_input_1_v_frmbuf_wr_1: v_frmbuf_wr@a0030000 {

#dma-cells = <1>;

clock-names = "ap_clk";

clocks = <&misc_clk_0>;

compatible = "xlnx,v-frmbuf-wr-2.1", "xlnx,axi-frmbuf-wr-v2.1";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 107 4>;

reg = <0x0 0xa0030000 0x0 0x10000>;

reset-gpios = <&gpio 92 1>;

};

The user need to add the input and output port information like below in the existing nodes(which is highlighted in blue)

hdmi_input_1_v_hdmi_rx_ss_0: v_hdmi_rx_ss@a0020000 {

compatible = "xlnx,v-hdmi-rx-ss-3.1", "xlnx,v-hdmi-rx-ss-3.1";

hdmirx_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

hdmirx_port1: port@0 {

/* Fill the fields xlnx,video-format and xlnx,video-width based on user requirement */

reg = <0>;

xlnx,video-format = <0>;

xlnx,video-width = <10>;

hdmi_rx_out1: endpoint {

remote-endpoint = <&vpss_scaler_in1>;

};

};

};

};

hdmi_input_1_v_proc_ss_0: v_proc_ss@a0200000 {

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

vpss_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

vpss_port01: port@0 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <0>;

xlnx,video-format = <12>;

xlnx,video-width = <8>;

vpss_scaler_in1: endpoint {

remote-endpoint = <&hdmi_rx_out1>;

};

};

vpss_port11: port@1 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <1>;

xlnx,video-format = <12>;

xlnx,video-width = <8>;

vpss_scaler_out1: endpoint {

remote-endpoint = <&vcap_hdmi_in1>;

};

};

};

};

The below vcap_hdmi1 node should be under the amba_pl: amba_pl@0 node

vcap_hdmi1 {

compatible = "xlnx,video";

dma-names = "port0";

dmas = <&hdmi_input_1_v_frmbuf_wr_1 0>;

vcap_hdmi_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

vcap_hdmi_port1: port@0 {

direction = "input";

reg = <0>;

vcap_hdmi_in1: endpoint {

remote-endpoint = <&vpss_scaler_out1>;

};

};

};

};

Case 2)For example the design have two similar video pipelines like sdi_rx → scaler → frmbuf_wr

The nodes for these IPs and their input and output ports are as below and this will be generated by the DTG.

1)sdi_rx IP

sdi_rx_input1_v_smpte_uhdsdi_rx_ss: v_smpte_uhdsdi_rx_ss@a0000000 {

compatible = "xlnx,v-smpte-uhdsdi-rx-ss-2.0", "xlnx,v-smpte-uhdsdi-rx-ss";

sdirx_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

sdirx_port: port@0 {

/* Fill the fields xlnx,video-format and xlnx,video-width based on user requirement */

reg = <0>;

xlnx,video-format = <0>;

xlnx,video-width = <10>;

sdi_rx_out: endpoint {

remote-endpoint = <&scaler_in>;

};

};

};

};

2)Scaler IP

sdi_rx_input1_v_proc_ss_0: v_proc_ss@a00c0000 {

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

scaler_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

scaler_port0: port@0 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <0>;

xlnx,video-format = <12>;

xlnx,video-width = <10>;

scaler_in: endpoint {

remote-endpoint = <&sdi_rx_out>;

};

};

scaler_port1: port@1 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <1>;

xlnx,video-format = <12>;

xlnx,video-width = <10>;

scaler_out: endpoint {

remote-endpoint = <&vcap_csi_in>;

};

};

};

};

3) framebuf_wr IP

sdi_rx_input0_v_frmbuf_wr_0: v_frmbuf_wr@b0000000 {

compatible = "xlnx,v-frmbuf-wr-2.1", "xlnx,axi-frmbuf-wr-v2.1";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 92 4>;

reg = <0x0 0xb0000000 0x0 0x10000>;

reset-gpios = <&gpio_resets_axi_gpio_resets 1 0 1>;

xlnx,vid-formats = "rgb888", "bgr888", "xbgr8888", "xrgb8888", "xbgr2101010", "uyvy", "y8", "y10", "vuy888", "xvuy8888", "yuvx2101010", "yuyv", "nv12", "nv16", "xv20", "xv15";

xlnx,video-width = <10>;

};

vcap_sdi {

compatible = "xlnx,video";

dma-names = "port0";

dmas = <&sdi_rx_input0_v_frmbuf_wr_0 0>;

vcap_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

vcap_port: port@0 {

direction = "input";

reg = <0>;

vcap_csi_in: endpoint {

remote-endpoint = <&scaler_out>;

};

};

};

};

For the second video pipeline DTG wont be generated the input and output port information and the nodes will be as below

sdi_rx_input0_v_smpte_uhdsdi_rx_ss: v_smpte_uhdsdi_rx_ss@a0030000 {

compatible = "xlnx,v-smpte-uhdsdi-rx-ss-2.0", "xlnx,v-smpte-uhdsdi-rx-ss";

interrupt-names = "sdi_rx_irq";

interrupt-parent = <&gic>;

interrupts = <0 89 4>;

reg = <0x0 0xa0030000 0x0 0x10000>;

};

sdi_rx_input0_v_proc_ss_0: v_proc_ss@a0080000 {

clock-names = "aclk_axis", "aclk_ctrl";

clocks = <&zynqmp_clk 72>, <&zynqmp_clk 71>;

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

};

sdi_rx_input1_v_frmbuf_wr_0: v_frmbuf_wr@b0020000 {

clock-names = "ap_clk";

clocks = <&zynqmp_clk 72>;

compatible = "xlnx,v-frmbuf-wr-2.1", "xlnx,axi-frmbuf-wr-v2.1";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 107 4>;

reg = <0x0 0xb0020000 0x0 0x10000>;

reset-gpios = <&gpio_resets_axi_gpio_resets 1 0 1>;

};

The user need to add the input and output port information something like this in the existing nodes(highlighted in blue)

sdi_rx_input0_v_smpte_uhdsdi_rx_ss: v_smpte_uhdsdi_rx_ss@a0030000 {

compatible = "xlnx,v-smpte-uhdsdi-rx-ss-2.0", "xlnx,v-smpte-uhdsdi-rx-ss";

interrupt-names = "sdi_rx_irq";

interrupt-parent = <&gic>;

interrupts = <0 89 4>;

reg = <0x0 0xa0030000 0x0 0x10000>;

sdirx_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

sdirx_port1: port@0 {

/* Fill the fields xlnx,video-format and xlnx,video-width based on user requirement */

reg = <0>;

xlnx,video-format = <0>;

xlnx,video-width = <10>;

sdi_rx_out1: endpoint {

remote-endpoint = <&scaler_in1>;

};

};

};

};

sdi_rx_input0_v_proc_ss_0: v_proc_ss@a0080000 {

clock-names = "aclk_axis", "aclk_ctrl";

clocks = <&zynqmp_clk 72>, <&zynqmp_clk 71>;

compatible = "xlnx,v-proc-ss-2.0", "xlnx,v-vpss-scaler-1.0", "xlnx,vpss-scaler";

scaler_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

scaler_port01: port@0 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <0>;

xlnx,video-format = <12>;

xlnx,video-width = <10>;

scaler_in1: endpoint {

remote-endpoint = <&sdi_rx_out1>;

};

};

scaler_port11: port@1 {

/* For xlnx,video-format user needs to fill as per their requirement */

reg = <1>;

xlnx,video-format = <12>;

xlnx,video-width = <10>;

scaler_out1: endpoint {

remote-endpoint = <&vcap_csi_in1>;

};

};

};

};

The below vcap_sdi1 node should be under the amba_pl: amba_pl@0 node

vcap_sdi1 {

compatible = "xlnx,video";

dma-names = "port0";

dmas = <&sdi_rx_input1_v_frmbuf_wr_0 0>;

vcap_ports1: ports {

#address-cells = <1>;

#size-cells = <0>;

vcap_port1: port@0 {

direction = "input";

reg = <0>;

vcap_csi_in1: endpoint {

remote-endpoint = <&scaler_out1>;

};

};

};

Case 3)For example the design have two similar video pipelines like sdi_tx → mixer → frmbuf_rd

The nodes for these IPs and their input and output ports are as below and this will be generated by the DTG.

1)sdi_tx IP

sdi_tx_output1_v_smpte_uhdsdi_tx_ss: v_smpte_uhdsdi_tx_ss@a0200000 {

compatible = "xlnx,v-smpte-uhdsdi-tx-ss-2.0", "xlnx,sdi-tx";

interrupt-names = "sdi_tx_irq";

interrupt-parent = <&gic>;

interrupts = <0 105 4>;

reg = <0x0 0xa0200000 0x0 0x20000>;

encoder_sdi_port: port@0 {

reg = <0>;

sdi_encoder: endpoint {

remote-endpoint = <&mixer_crtc>;

};

};

};

2)mixer IP

sdi_tx_output1_v_mix_0: v_mix@a0010000 {

compatible = "xlnx,v-mix-3.0", "xlnx,mixer-3.0";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 108 4>;

reg = <0x0 0xa0010000 0x0 0x10000>;

xlnx,bpc = <8>;

xlnx,num-layers = <4>;

xlnx,ppc = <2>;

crtc_mixer_port: port@0 {

reg = <0>;

mixer_crtc: endpoint {

remote-endpoint = <&sdi_encoder>;

};

};

xx_mix_master: layer_0 {

dma-names = "dma0";

dmas = <&sdi_tx_output1_v_frmbuf_rd_0 0>;

xlnx,layer-id = <0>;

xlnx,layer-max-height = <2160>;

xlnx,layer-max-width = <3840>;

xlnx,layer-primary ;

xlnx,layer-streaming ;

xlnx,vformat = "NV16";

};

xx_mix_overlay_1: layer_1 {

xlnx,layer-alpha ;

xlnx,layer-id = <1>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "NV12";

};

xx_mix_overlay_2: layer_2 {

xlnx,layer-alpha ;

xlnx,layer-id = <2>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "NV12";

};

xx_mix_overlay_3: layer_3 {

xlnx,layer-alpha ;

xlnx,layer-id = <3>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "AR24";

};

xx_mix_logo: logo {

xlnx,layer-id = <4>;

xlnx,layer-max-height = <64>;

xlnx,layer-max-width = <64>;

};

};

For the second video pipeline DTG wont be generated the input and output port information and the nodes will be as below

sdi_tx_output0_v_smpte_uhdsdi_tx_ss: v_smpte_uhdsdi_tx_ss@a0040000 {

compatible = "xlnx,v-smpte-uhdsdi-tx-ss-2.0", "xlnx,sdi-tx";

interrupt-names = "sdi_tx_irq";

interrupt-parent = <&gic>;

interrupts = <0 90 4>;

reg = <0x0 0xa0040000 0x0 0x20000>;

};

sdi_tx_output0_v_mix_0: v_mix@a0070000 {

clock-names = "ap_clk";

clocks = <&clk 72>;

compatible = "xlnx,v-mix-3.0", "xlnx,mixer-3.0";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 93 4>;

reg = <0x0 0xa0070000 0x0 0x10000>;

xlnx,bpc = <8>;

xlnx,num-layers = <4>;

xlnx,ppc = <2>;

};

The user need to add the input and output port information something like this in the existing nodes(highlighted in blue)

sdi_tx_output0_v_smpte_uhdsdi_tx_ss: v_smpte_uhdsdi_tx_ss@a0040000 {

compatible = "xlnx,v-smpte-uhdsdi-tx-ss-2.0", "xlnx,sdi-tx";

interrupt-names = "sdi_tx_irq";

interrupt-parent = <&gic>;

interrupts = <0 90 4>;

reg = <0x0 0xa0040000 0x0 0x20000>;

encoder_sdi_port1: port@0 {

reg = <0>;

sdi_encoder1: endpoint {

remote-endpoint = <&mixer_crtc1>;

};

};

};

sdi_tx_output0_v_mix_0: v_mix@a0070000 {

clock-names = "ap_clk";

clocks = <&clk 72>;

compatible = "xlnx,v-mix-3.0", "xlnx,mixer-3.0";

interrupt-names = "interrupt";

interrupt-parent = <&gic>;

interrupts = <0 93 4>;

reg = <0x0 0xa0070000 0x0 0x10000>;

xlnx,bpc = <8>;

xlnx,num-layers = <4>;

xlnx,ppc = <2>;

crtc_mixer_port1: port@0 {

reg = <0>;

mixer_crtc1: endpoint {

remote-endpoint = <&sdi_encoder1>;

};

};

xx_mix_master1: layer_0 {

dma-names = "dma0";

dmas = <&sdi_tx_output0_v_frmbuf_rd_0 0>;

xlnx,layer-id = <0>;

xlnx,layer-max-height = <2160>;

xlnx,layer-max-width = <3840>;

xlnx,layer-primary ;

xlnx,layer-streaming ;

xlnx,vformat = "NV16";

};

xx_mix_overlay_11: layer_1 {

xlnx,layer-alpha ;

xlnx,layer-id = <1>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "NV12";

};

xx_mix_overlay_21: layer_2 {

xlnx,layer-alpha ;

xlnx,layer-id = <2>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "NV12";

};

xx_mix_overlay_31: layer_3 {

xlnx,layer-alpha ;

xlnx,layer-id = <3>;

xlnx,layer-max-width = <1920>;

xlnx,vformat = "AR24";

};

xx_mix_logo1: logo {

xlnx,layer-id = <4>;

xlnx,layer-max-height = <64>;

xlnx,layer-max-width = <64>;

};

};

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy