...

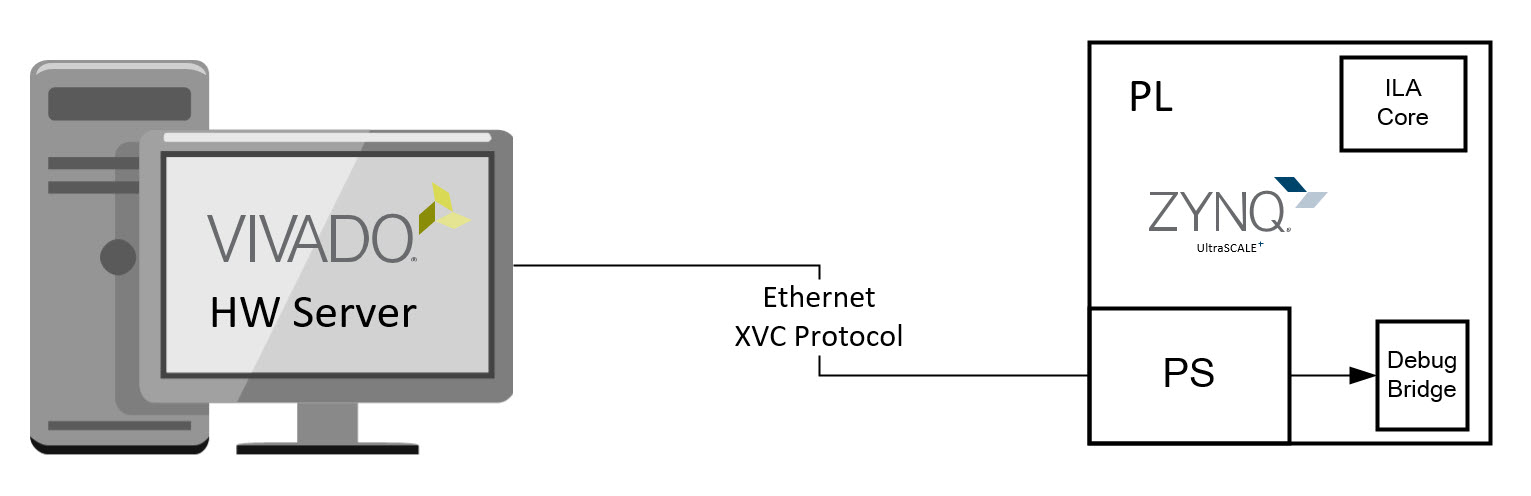

The Xilinx Virtual Cable (XVC) is a TCP/IP-based protocol that acts like a JTAG cable and provides a means to access and debug your FPGA or SoC design without using a physical cable. This enables a user to access a Xilinx device through another medium (In this case we use Ethernet) instead of needing a dedicated JTAG cable. This can be advantageous for in-field debugging or during stress test scenarios where JTAG is not an option.

Background

The Xilinx Virtual Cable started as an application note, XAPP1251, a number of years ago. Since that time, the solution has evolved to be cleaner and simpler using IP available in Vivado and source code from a GitHub repository. This wiki page is designed to be an update to the application note without duplicating information that has not changed.

One of the major differences in the implementation between XAPP1251 and this article, is location of the target FPGA. In XAPP1251 the target FPGA was another device and it was being accessed via JTAG pins from GPIO of the master FPGA. In this wiki article, the Target FPGA is the Programmable Logic within the Zynq/ZynqMP SoC device. This primary difference was enabled with the introduction of the Debug Bridge IP within the IP Catalog.

Expectations

This wiki page is intended to illustrate details of the Xilinx Virtual Cable but is not intended to be a tutorial for any of the tools that are used such as Vivado and PetaLinux. Users are expected to have background knowledge of Linux, embedded systems, and networking.

This wiki page will not describe XVC over PCIe. XVC over PCIe is more common in a data center application where there is a PCIe accelerator card. The concept is similar to what is described in this wiki page, but rather than Ethernet, PCIe is used.

Tools

The 2020.1 version of Xilinx tools including Vivado and PetaLinux were used for the prototype build of the hardware and software.

...