This section covers what Xilinx boards and peripherals are implemented in QEMU.

The following table shows what boards are supported by QEMU, and the names of the BSPs in PetaLinux and Yocto.

| Platform | Board Name | PetaLinux-specific Board Name | Yocto-specific board name |

|---|

| Artix-7 w/ Microblaze | AC701 | xilinx-ac701 |

|

| Kintex-7 w/ Microblaze | KC705 | xilinx-kc705 |

|

| Kintex-7 w/ Microblaze | KCU105 | xilinx-kcu105 |

|

| Spartan-7 w/ Microblaze | SP701 | xilinx-sp701 |

|

| Virtex Ultrascale+ w/ Microblaze | VCU118 | xilinx-vcu118 |

|

Zynq7000 SoC | ZC702 | xilinx-zc702 | zc702-zynq7 |

| Zynq7000 SoC | ZC706 | xilinx-zc706 | zc706-zynq7 |

Zynq Ultrascale+ | ZC1751 | xilinx-zc1751 |

|

| Zynq Ultrascale+ | ZCU102 | xilinx-zcu102 | zcu102-zynqmp |

| Zynq Ultrascale+ | ZCU104 | xilinx-zcu104 | zcu104-zynqmp |

| Zynq Ultrascale+ | ZCU111 | xilinx-zcu111 | zcu111-zynqmp |

| Zynq Ultrascale+ | ZCU1275 | xilinx-zcu1275 | zcu1275-zynqmp |

| Zynq Ultrascale+ | ZCU1285 | xilinx-zcu1285 | zcu1285-zynqmp |

| Zynq Ultrascale+ | ZCU208 | xilinx-zcu208 | zcu216-zynqmp |

| Zynq Ultrascale+ | ZCU216 | xilinx-zcu216 | zcu216-zynqmp |

| Zynq Ultrascale+ | Ultra96 | xilinx-ultra96 | ultra96-zynqmp |

| Versal | VCK190 | xilinx-vck190 | vck190-versal |

| Versal | VCK5000 | xilinx-vck5000 |

|

| Versal | VMK180 | xilinx-vmk180 | vmk180-versal |

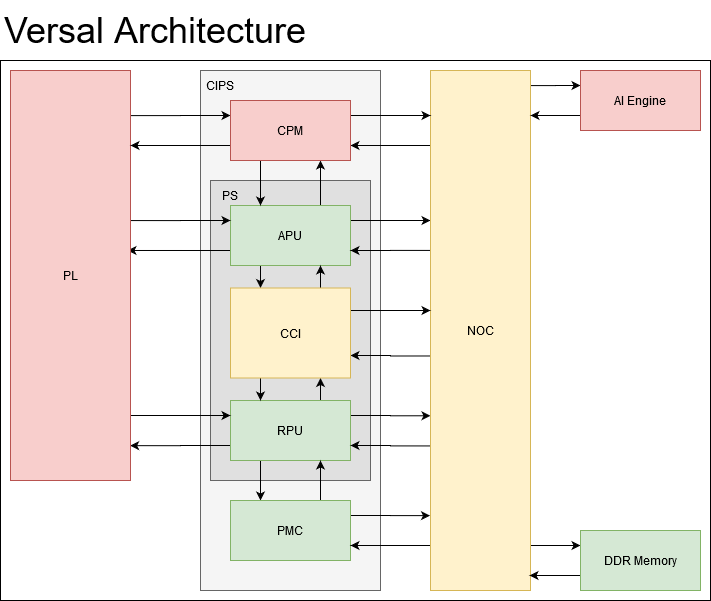

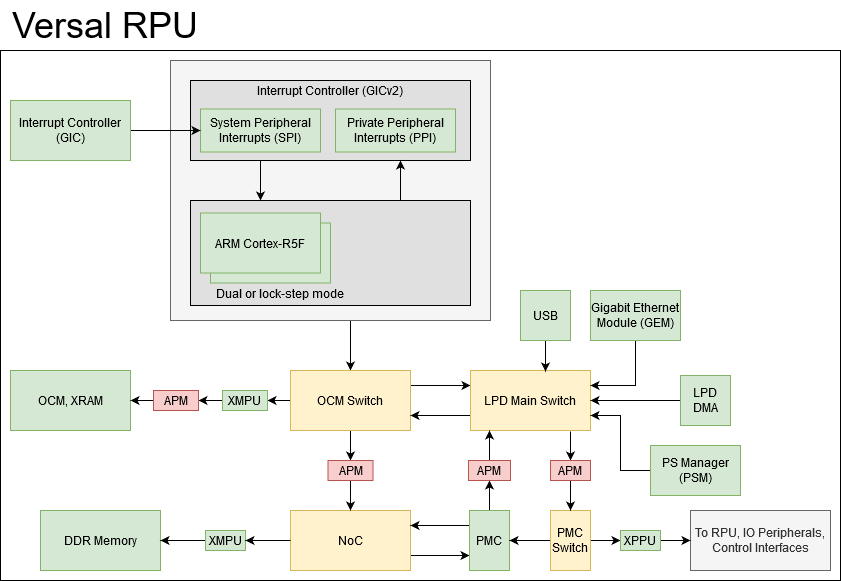

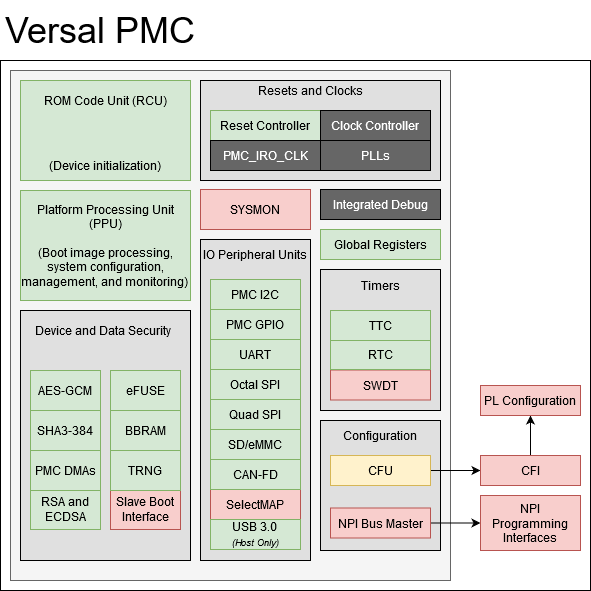

This section will cover what hardware and peripherals are supported in QEMU.

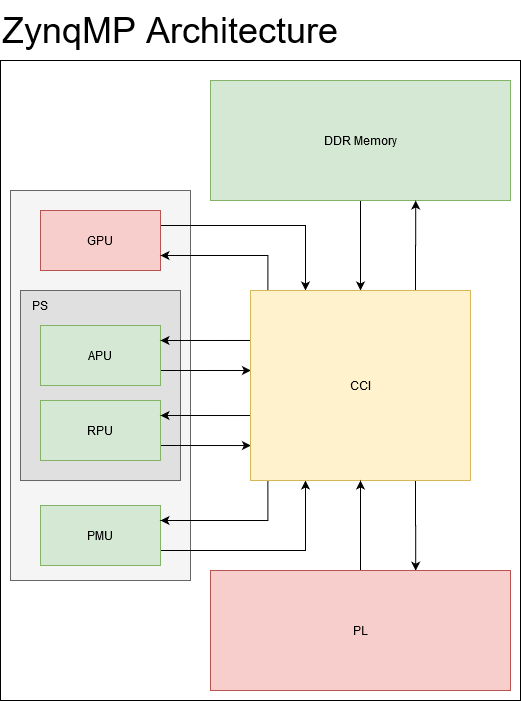

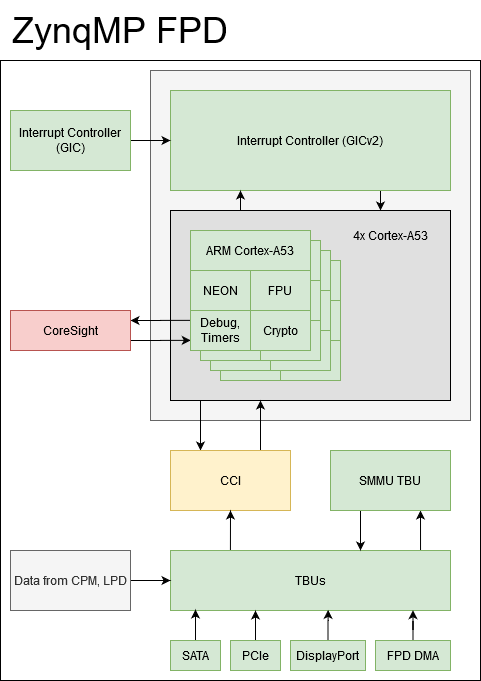

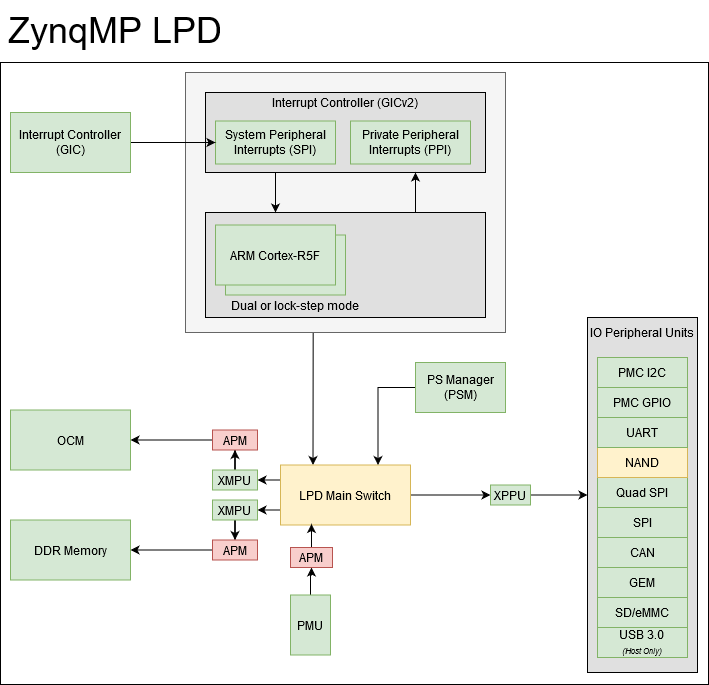

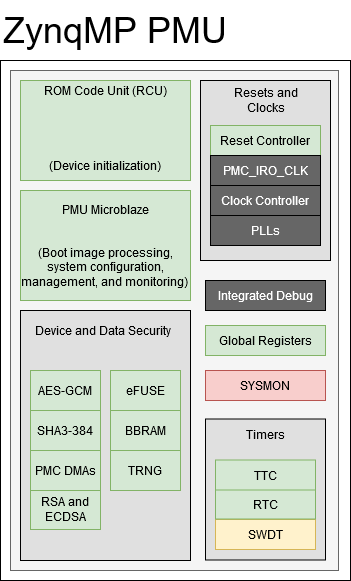

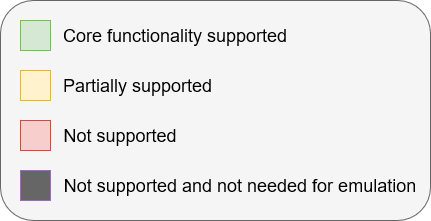

The block diagrams provide a broad overview of what is supported in each hardware block in QEMU, while the tables provide more detail on the support scope.

Supported Features Table

| Description | Support Scope |

|---|

| ARM Interrupt Controller (GICv2) | Supported |

| ARM v8 (A53) Implementation. | Little Endian Only |

| ARM v8 EL0 Support | AArch64 and AArch32 |

| ARM v8 EL1 Support | AArch64 and AArch32 |

| ARM v8 EL2 Support | AArch64 |

| ARM v8 EL3 Support | AArch64 |

| ARM v8 Crypto Instruction | Supported |

| Vector Floating Point (VFP) | As maintained by mainline. No formal acceptance criteria to feature |

| SIMD support | As maintained by mainline. No formal acceptance criteria to feature. |

| ARM v7 Support | A9, R5, R4 supported. |

| Description | Support Scope |

|---|

| Dual Core ARM-R5f | Incomplete coverage of system register set, little endian only |

| Dual core R5 CPU run-time configuration | Static dual core, no parallel/lock transitioning |

| Fault Handling | Faults can be externally injected |

| Tightly coupled Memories | Only globally accessible TCM memory region is accessible.

Flat memory only, no control register implementation |

| Interrupt Controller | Supported |

| SLCRs | Very limited functionality. Only dummy registers, except SD is_MMC control. |

| Description | Support Scope |

|---|

| IPI | Limited Connectivity specific to PMU functionality |

| Global Registers | Supported |

| PMU MicroBlaze | Supported |

| PMU Interrupt Controller | Supported |

| Description | Support Scope |

|---|

| I/O Peripherals | Not all peripherals are implemented.

Some standard peripherals are slight variations on the actual cores configuration-wise. |

| Cadence Gigabit Ethernet Controller | 1588 not supported. |

| SD Host Controller Interface (v3.0) | Supported |

| SD Card model | No SDXC |

| QSPI controller (excludes Linear and Generic) | Supported |

| QSPI linear region | No XIP. Slow emulation performance. |

| QSPI NOR flash devices | Incomplete but reasonable selection of parts including many modern QSPI capable devices. |

| OSPI | Supported |

| UART Controller | Supported |

| SPI controller | Master mode only. |

| I2C controller | Master mode only. |

| DDR | Simple flat RAM model, no ECC. |

| CAN | Supported |

| CAN-FD | Supported |

| XADC | Not supported |

| GPIO | Limited functionality, connects to remote port. |

| MDIO and Ethernet PHY | Dummy models, show link up on requested PHY using MDIO |

| USB | Supported - Host mode only. |

| SATA | Supported |

| PCI | Supported |

| Description | Support Scope |

|---|

| DP Model | AUX Communication.

DPCP: DisplayPort Configuration Information.

EDID. |

| DPDMA | Supported |

| 2 Layers | Supported |

| Alpha Blending | Supported |

| Audio | With some unexpected behavior |

| Dynamic resolution changes | Supported |

| Multiple pixel formats | Not all |

| Mali GPU | Not supported |

| Description | Support Scope |

|---|

| AMBA/AXI bus interconnect system | Simple bus model, no AXI/AMBA-specific features (such as MIDs).

Master IDs and Trustzone (secure versus non-secure) transactions supported. |

Bus quality of service monitoring and control

| N/A |

| On Chip Memory | Supported |

AXI Performance Monitor (APM)

AXI Trace Monitor (ATM)

| N/A |

| Description | Support Scope |

|---|

| XMPU | Does not return Slave error; CPU does not recognize asynchronous aborts on failed accesses. |

| XPPU | Does not return Slave error; CPU does not recognize asynchronous aborts on failed accesses. |

| SMMU | Only supports 64-bit page tables. |

| Clock/reset controllers for low-power and high power domains | Limited feature set specific to CPU functionality. |

| Interprocessor Interrupt controller | Supported |

| PL-based AMS block | N/A |

| Description | Support Scope |

|---|

| Ability to boot multiple software in different CPUs. | Supported |

| Create QEMU Machine models from Linux device tree binaries (DTB)s. | Limited to QEMU maintained DTBs only. IPI/HSI generated DTBs unsupported. |

| FPDDMA | No FCI and no rate-control. |

| LPDDMA | No FCI and no rate-control. |

| MTTCG | Supported |

| Description | Support Scope |

|---|

| Triple Timer Counter (TTC) | Supported |

| SWDT, WDT | Not Supported |

| Si570/71 | I2C device. Dummy emulation of clock generator. |

| RTC | Supported |

| Description | Support Scope |

|---|

| AES-GCM | Supported; all key sources |

| SHA3-384 | Supported |

| PMC DMAs | Supported |

| RSA | Supported |

| ECDSA | Supported |

| eFUSE | Supported; all documented fields |

| BBRAM | Supported |

| PUF | Supported. Limited to XilPuf API (Versal) and XilSkey API (ZynqMP). Helper-data usable across all QEMU sessions, all user credentials, and all hosts. |

| TRNG | Supported. Caveat, TRNG generation is statistically unsecured. |