Table of Contents

Introduction

The information on this page is specific to Zynq-7000 SoC devices. The Zynq-7000 Programmable Logic (PL) can be programmed either using First Stage Boot-loader (FSBL), U-Boot or through Linux.

This page provides the details about programming the PL from Linux world.

References:

https://github.com/Xilinx/linux-xlnx/blob/master/Documentation/fpga/fpga-mgr.txt

https://github.com/Xilinx/linux-xlnx/blob/master/Documentation/devicetree/bindings/fpga/fpga-region.tx

HW IP Features

- Full-Bitstream and partial Bitstream loading.

- Encrypted and Authenticated Bitstream loading.

Features supported in the Driver

- Full-Bitstream Bitstream loading.

- Encypted Bistream loading with Device-Key

Missing Features, Known Issues and Limitations

- No support for partial Bitstream loading.

- No support for Authenticated and Encrypted Bitstream loading.

- It is capable of loading only .bin format files into PL. It does not support any other file format.

NOTE:

The descriptions in subsequent sections refer to use of Device Tree Overlay (DTO) fragments with FPGA manager framework. It has to be noted that the generation of DTO fragments are not supported in official Xilinx Petalinux release.

Below sections describe steps for manual creation of pl.dtsi (contains the DTO fragment) to be used along with Xilinx 2018.3 Linux.

Kernel Configuration

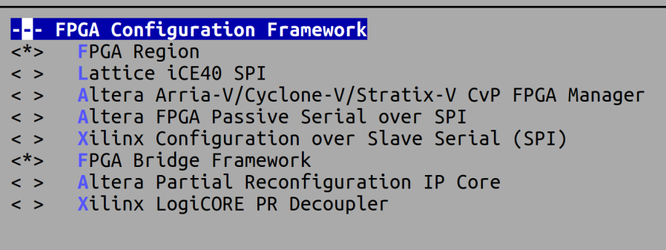

The following config options should be enabled in order to use FPGA Manager (In zynq_defconfig this options are enabled by default)Zynq FPGA Manager Configuration:

Select: Device Drivers ---> FPGA Configuration Framework

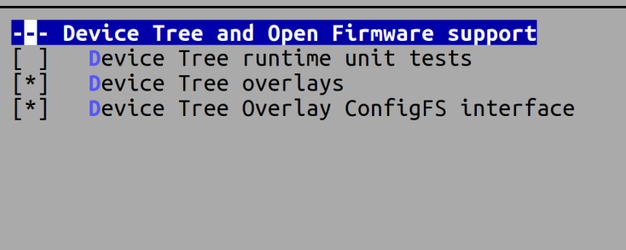

DT overlay ConfigFS interface Configuration:

This is required only if the user is using to the Bitstream using DTO

Select: Device Drivers --> Device Tree and Open Firmware support