| Date |

Version |

Author |

Description of Revisions |

| April 30 2014 |

1.0 |

Faster Technology |

Initial posting |

| Date |

Author |

Comment |

|

|---|---|---|---|

| Implementation Details |

|

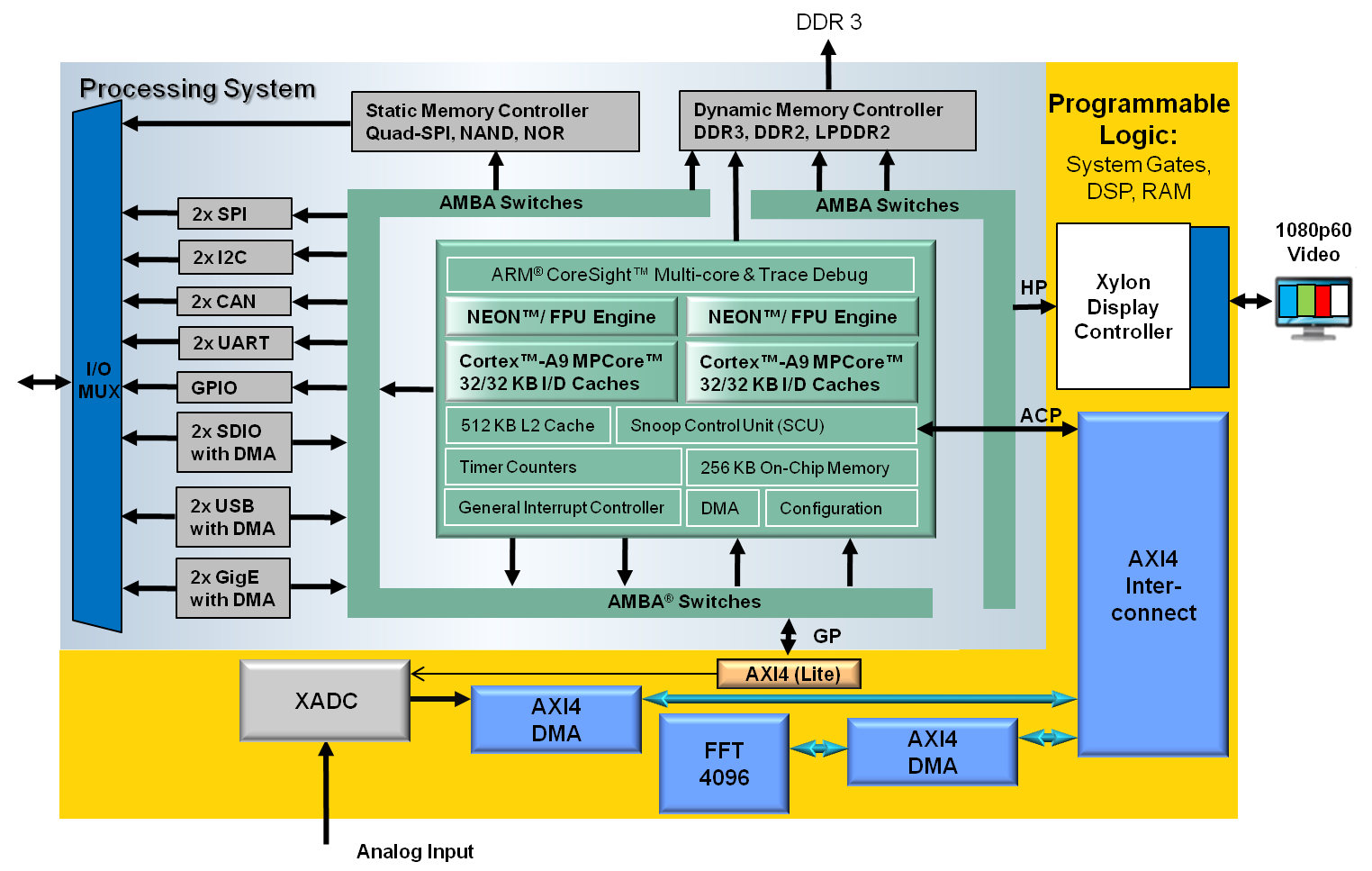

| Design Type |

PS & PL |

| SW Type |

Linux |

| CPUs |

Both ARM processors at standard ZC702 frequencies |

| PS Features |

Uses all standard PS features to run embedded Linux |

| PL Cores |

Video processing cores, XADC support core, AXI interconnect, FFT core from core generator, AXI DMA core |

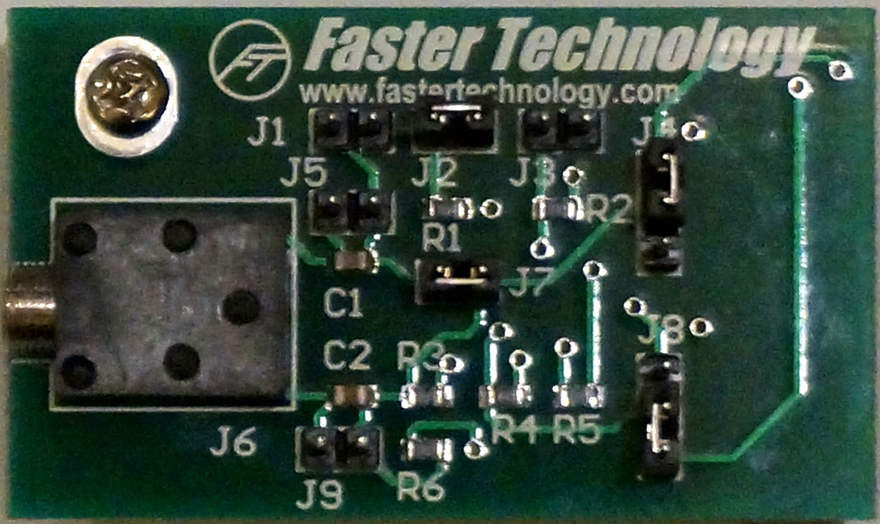

| Boards/Tools |

ZC702 and XA-2 headphone input adapter from Faster Technology |

| Xilinx Tools Version |

Built with Vivado / SDK 2013.4 and base TRD |

| Other Details |

Requires standard ZC702 power supply and cables; an HDMI monitor supporting 1920 X 1080P is required for video output |

| Files Provided |

|

| **ZC702FFTdemo.zip** |

SD card image |

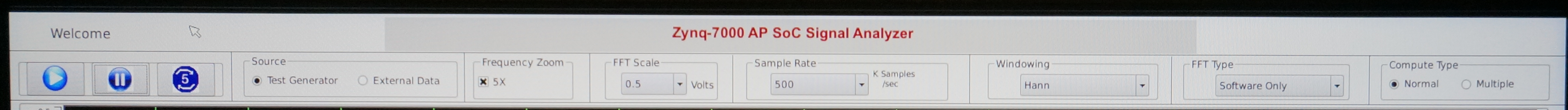

Play, Pause, Pause 5 seconds repeatedly

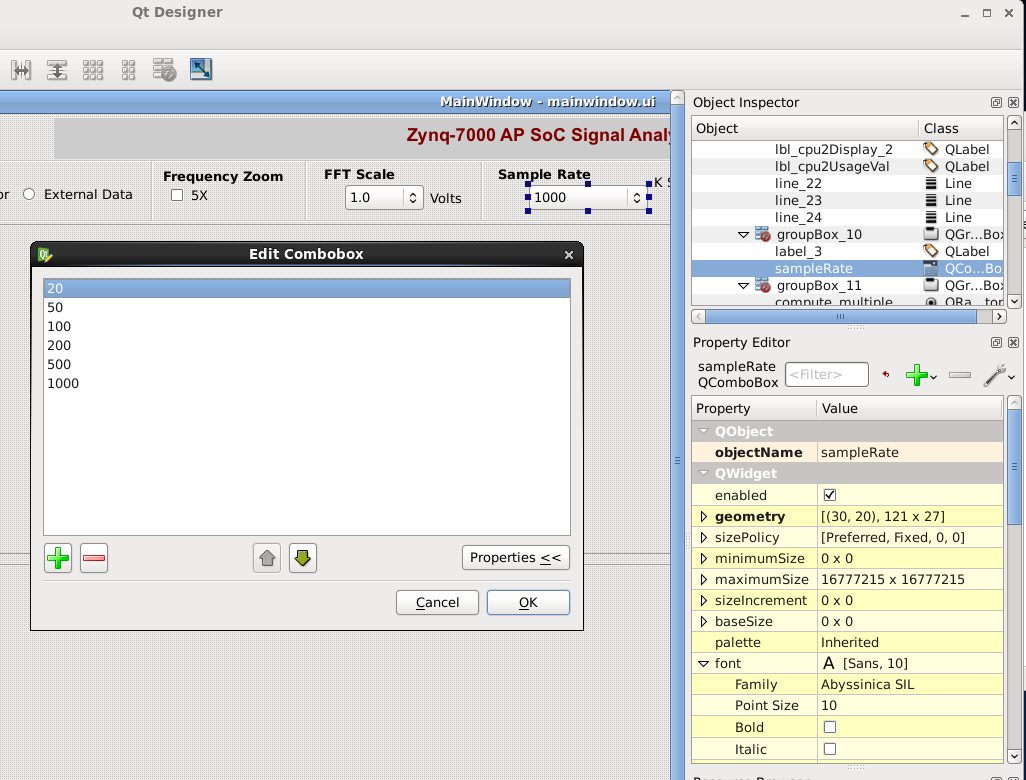

Play, Pause, Pause 5 seconds repeatedly Select vertical scale (max value) FFT display - 0.1, 0.25, 0.5 or 1.0 volts - enhances low level signals

Select vertical scale (max value) FFT display - 0.1, 0.25, 0.5 or 1.0 volts - enhances low level signals Sample Rate - select the XADC sample rate (20, 50, 100, 200 5001000 K Samples / sec.)

Sample Rate - select the XADC sample rate (20, 50, 100, 200 5001000 K Samples / sec.) Windowing - select none or a common FFT window (http://en.wikipedia.org/wiki/Window_function)

Windowing - select none or a common FFT window (http://en.wikipedia.org/wiki/Window_function) FFT Compute resource - Software, NEON, PL Accelerated (See yellow status window for average compute time)

FFT Compute resource - Software, NEON, PL Accelerated (See yellow status window for average compute time) Compute Type - Normal / Multiple - multiple reads and computes 1000 FFTs and then displays the last computed value. Useful for seeing relative update performance and CPU loading.

Compute Type - Normal / Multiple - multiple reads and computes 1000 FFTs and then displays the last computed value. Useful for seeing relative update performance and CPU loading. Status Window - displays average compute time for the FFT - depends on FFT type selected.

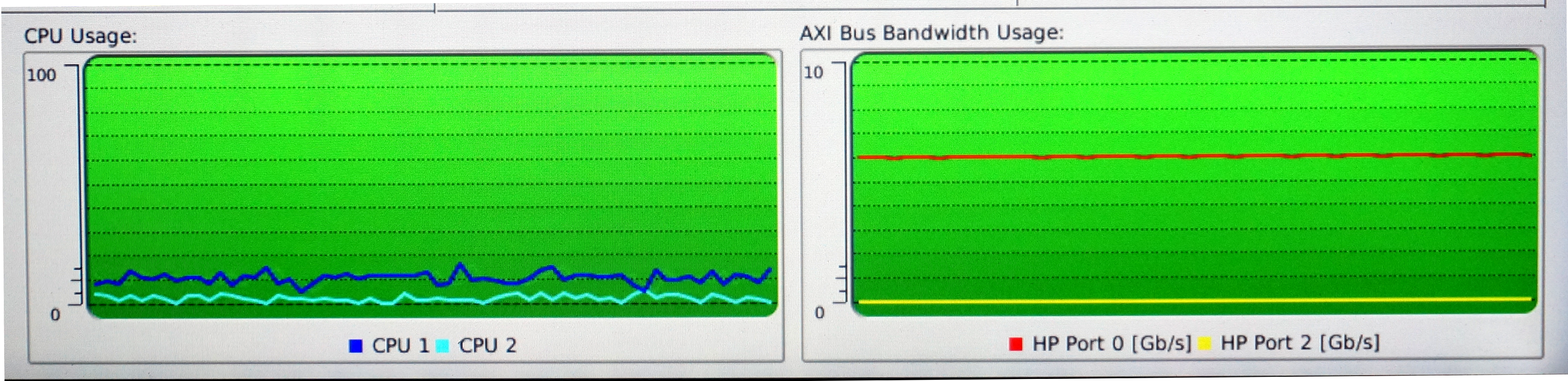

Status Window - displays average compute time for the FFT - depends on FFT type selected. Performance - shows the CPU loading and use of the HP ports between the PS and PL

Performance - shows the CPU loading and use of the HP ports between the PS and PL Block Diagram shows the data flow in the application - changes based on selected input and FFT type

Block Diagram shows the data flow in the application - changes based on selected input and FFT type Usage - graphically shows CPU and AXI bus loading

Usage - graphically shows CPU and AXI bus loading