Table of Contents

Introduction

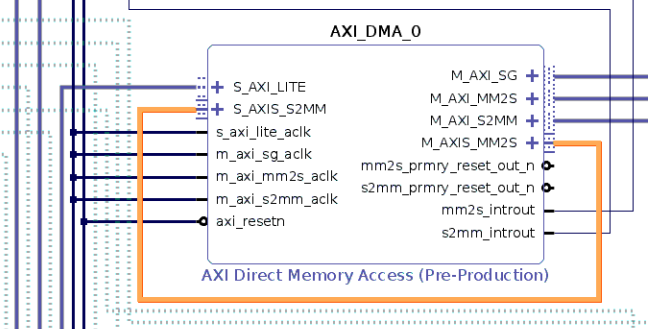

The AXI DMA core is a soft Xilinx IP core for use with the Xilinx Vivado® Design Suite. The AXI DMA provides high-bandwidth direct memory access between memory and AXI4-Stream target peripherals. Its optional scatter/gather capabilities also offload data movement tasks from the Central Processing Unit (CPU).

For more information, please refer to the AXI DMA product page which includes links to the official documentation and resource utilization.

Driver Sources

The source code for the driver is included with the Vitis Unified Software Platform installation, as well as being available in the Xilinx Github repository.

| Driver Name | Path in Vitis | Path in Github |

|---|---|---|

| axidma | <Vitis Install Directory>/data/embedded/XilinxProcessorIPLib/drivers/axidma_<version> | https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/axidma |

Note: To view the sources for a particular release, use the rel-version tag in github. For example, for the 2020.1 release, the proper version of the code is: https://github.com/Xilinx/embeddedsw/tree/xilinx-v2020.1/XilinxProcessorIPLib/drivers/axidma |

The driver source code is organized into different folders. The table below shows the axidma driver source organization.

| Directory | Description |

|---|---|

| doc | Provides the API and data structure details |

| data | Driver .tcl, .mdd file and .yaml files |

| examples | Example applications that show how to use the driver features |

| src | Driver source files, make and cmake files |

Note: AMD Xilinx embeddedsw build flow is changed from 2023.2 release to adapt to the new system device tree based flow. For further information, refer to the wiki page Porting embeddedsw components to system device tree (SDT) based flow - Xilinx Wiki - Confluence (atlassian.net).

The .yaml(in data folder) and CMakeLists.txt(in src folder) files are needed for the System Device Tree based flow. The Driver .tcl and .mdd files are for the older build flow which will be deprecated in the future.

Driver Implementation

For a full list of features supported by this IP, please refer to the AXI DMA product page.

Features

The AXI DMA Standalone driver supports the following features: - Simple DMA mode

- Scatter/Gather Direct Memory Access (DMA)

- multi-channel operation (up to 16 channels)

- 64-bit Addressing

- Key Hole Feature

- Optional Data Re-Alignment Feature

Known Issues and Limitations

The following is a list of known limitations of the driver and features of the IP that are not currently implemented:

- No Support for Cyclic DMA mode.

- When H/w is configured without DRE driver will throw an error if the user sends an unaligned error.

- User application should handle buffer address alignment in case h/w is configured without DRE

Example Design Architecture

The examples assumes AXIDMA is

Example Applications

Refer to the driver examples directory for various example applications that exercise the different features of the driver. Each application is linked in the table below. The following sections describe the usage and expected output of the various applications. These example applications can be imported into the Vitis IDE from the Board Support Package settings tab.

Links to Examples

Examples Path: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/axidma/examples

| Test Name | Example Source | Description |

|---|---|---|

| Self Test | xaxidma_example_selftest.c | This example does a basic reset of the core and checks core is coming out of reset or not. |

| Scatter Gather DMA with Interrupts | xaxidma_example_sg_intr.c | This example demonstrates how to transfer packets in interrupt mode when the core is configured in Scatter Gather Mode. |

| Scatter Gather DMA with Polling | xaxidma_example_sg_poll.c | This example demonstrates how to transfer packets in the scatter gather polled mode. |

| Simple DMA with Interrupt | xaxidma_example_simple_intr.c | This example demonstrates how to transfer packets in interrupt mode when the core is configured in Simple DMA Mode. |

| Simple DMA with Polling | xaxidma_example_simple_poll.c | This example demonstrates how to transfer packets in the polled mode when the core is configured in Simple DMA Mode. |

| SGDMA Multi-Packet Polled Mode | xaxidma_example_poll_multi_pkts.c.c | This example demonstrates how to transfer multiple packets in the polled mode when the core is configured in Scatter Gather Mode. |

| Scatter Gather DMA with Interrupts in cyclic mode | xaxidma_example_sgcyclic_intr.c | This example demonstrates how to transfer packets in cyclic mode where the same buffer descriptors are processed continuously by the DMA. This is demonstrated in interrupt mode when the core is configured in Scatter Gather Mode. |

Example Application Usage

Self Test

This example does a basic reset of the core and checks core is coming out of reset or not.

Expected Output

--- Entering main() --- Successfully ran AxiDMASelfTest Example --- Exiting main() -- |

Scatter Gather with Interrupts

This example demonstrates how to transfer packets in interrupt mode when the core is configured in Scatter Gather Mode.

Expected Output

--- Entering main() --- Successfully ran AXI DMA SG interrupt Example --- Exiting main() --- |

Scatter Gather with Polling

This example demonstrates how to transfer packets in the scatter gather polled mode.

Expected Output

--- Entering main() --- Successfully ran AXI DMA SG Polling Example --- Exiting main() --- |

Simple DMA with Interrupts

This example demonstrates how to transfer packets in interrupt mode when the core is configured in simple DMA mode.

Expected Output

--- Entering main() --- Successfully ran AXI DMA interrupt Example --- Exiting main() --- |

Simple DMA with Polling

This example demonstrates how to transfer packets in poll mode when the core is configured in simple DMA mode.

Expected Output

--- Entering main() --- Successfully ran XAxiDma_SimplePoll Example --- Exiting main() --- |

Scatter Gather Multi-Packet Polled Mode

This example demonstrates how to transfer multiple packets in poll mode when the core is configured in Scatter Gather Mode.

Expected Output

--- Entering main() --- Successfully ran AXI DMA poll multi Example --- Exiting main() --- |

Change Log

2023.2

https://github.com/Xilinx/embeddedsw/blob/xlnx_rel_v2023.2/doc/ChangeLog#L543

2023.1

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2023.1/doc/ChangeLog#L53

2022.2

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2022.2/doc/ChangeLog#L75

2022.1

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2022.1/doc/ChangeLog#L185

2021.2

None

2021.1

https://github.com/Xilinx/embeddedsw/blob/xilinx_v2021.1/doc/ChangeLog#L400

2020.2

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2020.2/doc/ChangeLog#L341

2020.1

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2020.1/doc/ChangeLog#L285

2019.2

https://github.com/Xilinx/embeddedsw/blob/xilinx-v2019.2/doc/ChangeLog#L167

Related Links