Table of Contents

Introduction

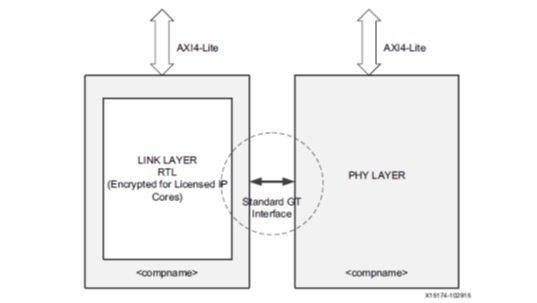

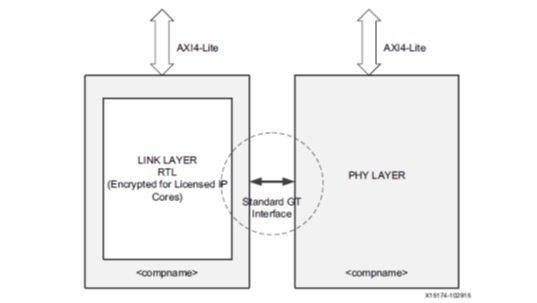

The Xilinx® Video PHY Controller LogiCORE™ IP core is designed for enabling plug-and-play connectivity with Video (DisplayPort and HDMI® technology) MAC Transmit or Receive subsystems. VideoPhy driver supports only HDMI protocol as of now.

The interface between the video MAC and PHY layers are standardized to enable ease of use in accessing shared transceiver resources. The AXI4-Lite register interface is provided to enable dynamic accesses of transceiver controls/status

Video IP Layer

Video IP LayerDriver Overview

The PHY is intended to simplify the use of serial transceivers and adds domain-specific configurability. The Video PHY Controller IP/Driver is not intended to be used as a stand alone IP and must be used with Xilinx Video MACs such as HDMI 1.4/2.0 Transmitter/Receiver Subsystems and DisplayPort TX/RX Subsystems.

As such PHY Linux Driver is implemented within the kernel PHY framework and is tightly coupled with HDMI Rx/Tx Linux drivers. This driver also hosts the common video files shared between the 3 Xilinx connectivity drivers (Vphy, HDMI Rx and HDMI Tx) and exports the relevant API’s for inter-driver communication. On kernel boot-up both HDMI Rx & Tx drivers will request 3 PHY lanes each for Rx & Tx and will defer until PNY driver has been initialized.

IP/Driver Features

| IP Feature | 2018.1 - 2019.1 | 2019.2 and onward | 2020.1 - 2023.2 |

| IP Version Supported | 2.2 | 2.2 | 2.2 |

AXI4-Lite support for register accesses | Y | Y | Y |

Protocol Support: Display Port, HDMI | Only HDMI | Only HDMI | DisplayPort and HDMI |

Full transceiver dynamic reconfiguration port (DRP) accesses and transceiver functions | Y | Y | Y |

Independent TX and RX path line rates (device specific) | Y | Y | Y |

Single quad support | Y | Y | Y |

Phase-locked loop (PLL) switching support from software | Y | Y | Y |

Transmit and Receiver user clocking | Y | Y | Y |

Protocol specific functions (For example, HDMI Clock Detector) | Y | Y | Y |

Non-integer data recovery unit (NI-DRU) support for lower line rates. NI-DRU support is for the HDMI protocol only. | Y | Y | Y |

Advanced Clocking Support | N | N | Y |

| Use of 4th GT channel as TX TMDS clock | N | Y | Y |

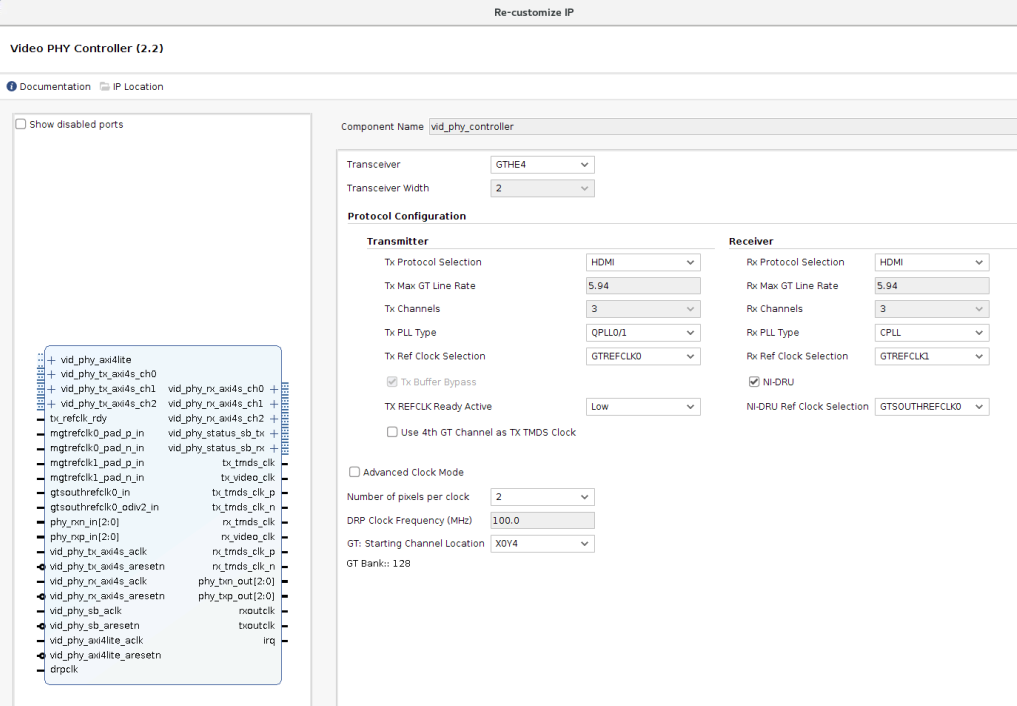

HW IP Configuration

Only below depicted IP configuration is supported at this time

Known Issues and Limitations

- Only 1 IP configuration supported (listed in HW IP Configuration section)

- Supports only HDMI protocol at this time

Kernel Configuration Options for Driver

2018.1 and onwards: CONFIG_ARCH_ZYNQMP and CONFIG_GENERIC_PHY should be enabled

Driver is added as an out-of-tree kernel module and therefore requires no driver specific kernel configuration However to enable the driver user must include it in the rootfs. Following steps are required enable the driver

- Make sure the meta-user layer has the recipe-hdmi included

- For 2019.2 onwards

CONFIG_kernel-module-hdmi |

- For 2018.1 to 2019.1

- Add the recipe to petalinux image. Edit ./meta-user/recipes-core/images/petalinux-image-full.bbappend and add the new recipe at the end

- NOTE - While using 2018.1 petalinux, the file name was ./meta-user/recipes-core/images/petalinux-image.bbappend

IMAGE_INSTALL_append = " kernel-module-hdmi" |

- Next include the driver in the rootfs

% petalinux-config -c rootfs |

- Select "user-pakages->modules->kernel-module-hdmi", save and exit

- Build the project

Device Tree Binding

The dts node should be defined with correct hardware configuration. How to define the node is documented in

2018.1: Documentation/devicetree/bindings/xlnx,vphy.txt DEBUG Capability

Video PHY Linux driver implements the capability to tap IP status at pre-defined points in the control flow. User can enable the debug taps by uncommenting the pre-processor directive (

#define DEBUG) to monitor the progress within the driver. All debug prints are sent to serial console and can be viewed in kernel

dmesg buffer

How to capture vphy state machine logs

Run below command to print the vphy state machine logs or vphy information

# For Logs, run anyone of the below. It will give logs for both TX and RX state machine logs of vphy. Do note that its a destructive logging. Once you run below command, the logs buffer will become empty.

cat /sys/devices/platform/amba_pl\@0/80080000.v_hdmi_tx_ss/vphy_info

or

cat /sys/devices/platform/amba_pl\@0/80000000.v_hdmi_rx_ss/vphy_log

# For vphy info, run below commands

cat /sys/devices/platform/amba_pl\@0/80080000.v_hdmi_tx_ss/vphy_log

or

cat /sys/devices/platform/amba_pl\@0/80000000.v_hdmi_rx_ss/vphy_info |

How to capture register dump

Create a script on target and name it as dumpmem.sh. Paste below content in that script.

#!/bin/sh

# Usage dumpmem.sh ADDR OFFSET

base=$1

counter=0

while [ $counter -lt $2 ];

do

offset=$(($counter*4))

reg_addr=$(($base + $offset))

reg_addr=`printf "0x%X\n" $reg_addr`

output=$(devmem $reg_addr)

delimiter=": "

echo $reg_addr$delimiter$output

counter=$(($counter+1))

done

echo All done |

Now run below command to dump the registers of Vphy

# In the below command, first parameter is the base address of the IP (vphy) in this case and second parameter is the number of registers to be read

./dumpmem.sh 0x80120000 206 |

Boards Supported

Driver has been tested on following boards

- zcu102 Rev 1.0

- Zcu106 Rev 1.0

Driver has been tested with HDMI FrameBuffer Example Design design

Change Log

2024.1

2023.2

2023.1

2022.2

2022.1

2021.2

2021.1

- Summary

- Update the phy driver based on bare metal driver updates to components like hdcp, video common library, etc.

- Commits

2020.2

- Summary

- Fix coverity warnings

- Remove GT workaround patch

- Add helpers to parse and generate HDR Aux packets

- Commits

2020.1

- Summary

- Add support for Versal Phy (HDMI GT controller) in same driver

- Add minor fixes and updates

- Fix sha

- Add VIC entries

- memset packet structure to 0 while generating

- Commits

2019.2

- Summary

- Driver updated for 2019.2

- Enabled TX 4th GT channel support

- Enabled suspend and resume

- Updated license file for 2019.2

- Commits

- be354c license: Update the license 2019.2

- c1d04e hdmi: Driver update till 20190906

- 55a308 phy: Enabling 4th GT channel in TX

- 7eeeb1 hdmitx:hdmirx:vphy: Enabling suspend and resume

- b608fb hdmitx:hdmirx:phy: remove "addtogroup" from files

- e8da36 hdmitx:hdmirx:vphy: Driver update till 20190814

2019.1

- Summary

- Made driver compliant with DTG tool generated Device tree nodes and updated the documentation.

- Updated license file for 2019.1

- Commits

- cf0a56 hdmitx: hdmirx: vphy: Driver update 5Apr2019

- fe84ed license: Update the license obtained from legal

- 3b3484 dt:bindings: Updated the documentation on DT bindings

- 947f4f tx: hdmirx: vphy: Driver update 14Mar2018

- e96b83 hdmitx:hdmirx:vphy: Support for auto DTG

2018.3

- Summary

- Made dru clock optional depending on NI-DRU configured value

- Commits

- 5d42de hdmitx:hdmirx:vphy:dt:bindings: Drivers update 20181004

- 1c0710 hdmitx:hdmirx:phy: Update driver version 20180817

- 309e4f phy: Enabling DRU clock

- f9994e hdmitx:hdmirx:phy: Updated driver IP version

- e7802d vphy: make dru optional

2018.1

- Summary

- Added 0.5% margin to user clock frequency

- Commits

- c443f3 phy: vphy: add 0.5% margin to user clock freq

- ebee44 Initial release of 2018.1 hdmi drivers as kernel modules

Related Links