Table of Contents

This documents provides driver details about the Xilinx DDR ECC controller driver used in Versal SOC.

Xilinx Versal DDR ECC Controller supports

Single bit error detection and correction

Double bit error detection.

Interrupt support.

Error injection support for both single bit and double bit errors.

In 2020.2, we are not supporting the DTG flow to generate final dt node for EDAC.

The following kernel configuration options should be enabled for compiling the Xilinx Versal EDAC driver.

CONFIG_EDAC=y

CONFIG_EDAC_VERSAL=y

Enable the "EDAC Debug" configuration under CONFIG_EDAC - This is required for error injection support.

CONFIG_EDAC_DEBUG=y

|

DDRMC with ECC enabled design

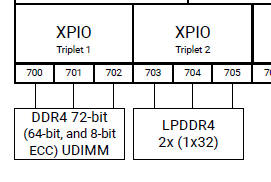

The controller supports LPDDR configurations with different bus widths, such as DDR4x72 , LP4 x40 and LP4 x24.

On vck190 we have 64 bit DDR but only 32 lines are connected in the current setup for LPDDR in vck190.

When ECC is enabled in LPDDR4 configurations and the memory is only 16 bits, the rest of the bits are used for ECC.

LP4x24 and DDR4x72 is there is vck190 and the same is tested. We do not have 40 line LPDDR connected in vck190 this is not

tested.

Mainlined

DT changes:

For 2020.2 release we are not supporting DTG flow, so user must enable the memory controller node in the DTS file based on the design.

in DTS file, whichever DDRMC controller(>=1) is enabled (DDRMC0-DDRMC4), change the status variable from "disabled" to "okay" in memory-controller node.

Kernel Boot log for EDAC driver

|

To reserve the test memory location for error injection

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

reserved: buffer@0 {

reusable;

reg =<0x0 0x2002000 0x0 0x00100000>;

};

};

reserved-driver@0 {

compatible = "xlnx,reserved-memory";

memory-region = <&reserved>;

};

|

Test logs for CE and UE errors injection:

|

None

None

None

ff817e4 - edac: xilinx: make event manager registration configurable

f179b8 - edac: xilinx: Fix kernel-doc for two functions

7d8a993 - driver: edac: Use error events header file in xilinx ddrmc driver

d2aa9a9 - Fix the error path

734c865 - Add support for registering for notification

d5a09f3 - enable the UE interrupt in IRQ1

043c48a - New driver added