Zynq UltraScale+ MPSoC Power Advantage Tool 2019.1

Zynq UltraScale+ MPSoC Power Advantage Tool 2019.1

Preliminary

Zynq UltraScale+ MPSoC Power Advantage Tool 2019.1

Now that you have installed and run the Pre-Built Power Advantage Tool, let’s take a moment to see what else you can do with it. The Power Advantage Tool Control Console can be used, with designs, to monitor power during the design process. In addition, the Power Advantage Tool can be used as a demonstration of the power savings with various designs.

Table of Contents

Document History

| Date | Version | Author | Description of Revisions |

| Jan 7, 2020 | jerrywo | Created |

1 Power Advantage Tool

Known 2019.1 Issues:

(1) The MSP430 source builds the compatible MSP430 version, but may not support all debug features.

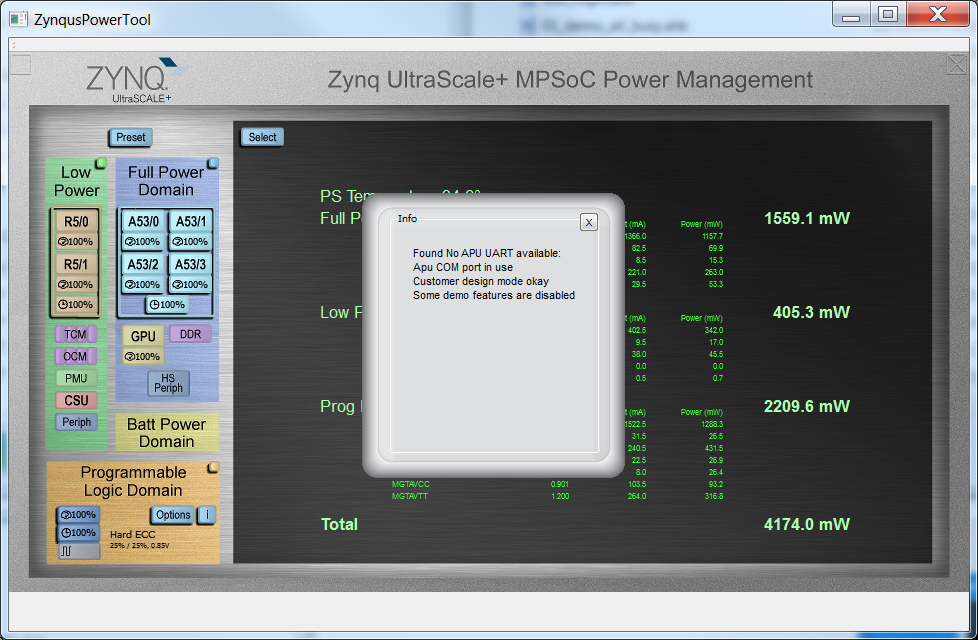

Note: The Power Advantage Tool now takes control of the APU serial port if available. To give user control of the APU terminal, close the Power Advantage Tool, then launch the following script to open terminals, then open the Power Advantage Tool again. The Power Advantage Tool will complain that "No APU UART available", but just close that message.

1.1 Launching the Power Advantage Tool Control Console

Warning: If you have connected Micro USB (UART) (J83) to PC for the first time, or switched boards, you may need to wait a few minutes for the PC to recognize the new hardware. Then you can open the Power Advantage Tool.Launch the Power Advantage Tool Shortcut at C:\ZynqUS_Demos\ZynqusPowerTool.exe Shortcut.

In a few seconds, you should see a Power Advantage Tool Control Console window with a Power Report. The Power numbers should update every few seconds.

If it is not displayed properly, refer to “Common Setup Issues”, and debug until the “Power Advantage Tool is alive” before returning here to continue.

1.2 Getting to Know the Power Advantage Tool Control Console

After successfully launching the Power Advantage Tool, you should see the following Power Advantage Tool Control Console window (may take a few seconds):

Figure 1. Power Advantage Tool Control Console

This interface is important to most of the demonstrations, so it would be good to familiarize yourself with it. Take a moment to identify the following:

- Zoom Display (transparent button [ ]) (A) resizes to fill a 1920x1080 display.

- Close (transparent button [X]) (B)

- Minimize (C)

- Select (D) Selects the display mode (Rails, Plot, About contains the version number)

- Preset (E) Places the ZCU102 into a selected state.

- Block Diagram of Zynq (F) shows the current device state.

- Power Totals for various domains (G) (Note: There can be a few seconds delay for measurement and update.)

Note: The Temperature is polled only every few seconds, so it appears after a short time.

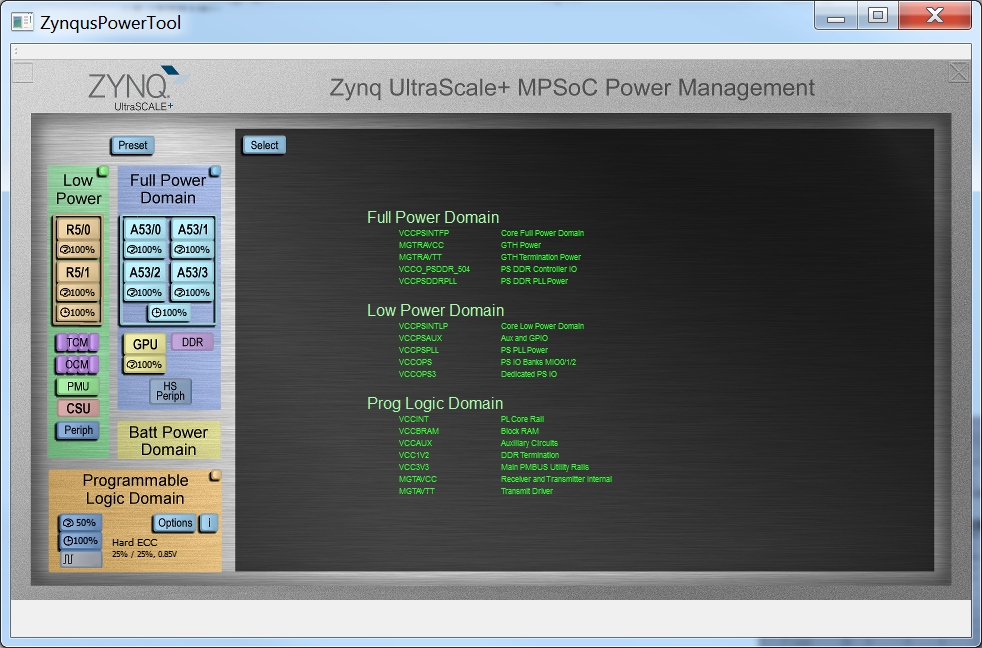

Here is a Table of the Rails for ZCU102:

- VCCPSINTFP – Core Full Power Domain

- MGTRAVCC – GTX Power

- MGTRAVTT – GTX Termination Power

- VCCO_PSDDR_504 – PS DDR Controller IO

- VCCPSDDRPLL – PS DDR PLL Power

- VCCPSINTLP – Core Low Power Domain

- VCCPSAUX – Aux and GPIO

- VCCPSPLL – PS PLL Power

- VCCOPS – PS IO Banks MIO0/1/2

- VCCOPS3 – Dedicated PS IO

- VCCINT – PL Operating

- VCCBRAM – Block RAM

- VCCAUX – Auxiliary Circuits

- VCC1V2 – DDR Termination

- VCC3V3 – Main PMBUS Utility Rails

- MGTAVCC – Receiver and Transmitter Internal

- MGTAVTT – Transmit Driver

It is a power advantage to be able to turn off unused circuitry. The more power islands and domains you have, the more flexibility you have to save power.

Islands are power switched internally to the Zynq UltraScale+ MPSoC, whereas Domains switch power rails externally to the Zynq device. When Domain switching can be done, this has the advantage of drawing no power by being able to completely turn off a portion of the silicon device.

Note: Switching off domains can clear the program memory until reboot.

Control can be over entire Domains or individual Islands. The next sections will demonstrate switching the Power Domains.

1.3 Domain Control

Power Domains are broad sections of the Zynq UltraScale+ MPSoC an d are the Full Power, Low Power, and Programmable Logic Domains.

The Power Advantage Tool requires no further setup to have access to the Power Domain Controls.

Figure 2. Power Domain Controls

With the Power Advantage Tool running, identify the following controls:

(A) Preset Button

(B) Low Power Domain Button

(C) FulI Power Domain Button

(D) Four A53 Processor Core Power Island Buttons

(E) Programmable Logic Domain Button

1.4 PL Control

The demo PL design is featured from the command line in section 1.6.

1.5 Selecting Displays

Pressing the Select button gives a menu to select from various displays:

- Plot: Graphically displays the power for each of the three domains and total power.

Figure 4. Plot.

- Rails: This is the default display. Rails displays the voltage and power for each of the rails, as well as the chip temperature, and the total power. The power measurements are made external to the Zynq by TI INA226 chips.

Figure 5. Rails.

- Sysmon: This displays the temperature and voltages read by the System Monitor on the Zynq.

Figure 6. Sysmon.

- Legend: This page defines each of the Zynq rails.

Figure 7. Legend.

- About: This page contains the legal notice, as well as the software revisions for Qt and MSP430 code.

Figure 8. About.

1.6 Linux

The Linux "PL Power Management Demo" is run from a Linux command line. The sources are provided with build instructions.

Note: This portion of the demo requires a user APU terminal. The Power Advantage Tool now takes control of the APU serial port if available. To give user control of the APU terminal, close the Power Advantage Tool, then launch the following script to open terminals, then open the Power Advantage Tool again. The Power Advantage Tool will complain that "No APU UART available", but just close that message.

From C:\ZynqUS_Demos\2019.1_Demos, launch 00a_open_terminals_ZCU102.ahk.

1.6.1 Launch PL Power Management

Login: root, Password: root

pl-power

By default, the PL is idle. With Idle, the PL power is about 760mW

This is the Static Power of the PL

1.6.2 Set PL to Full Performance

1 - Reprogram PL for Soft ECC Partial Bitstream

3 - Change Clock Frequency to ECC Modules

4 - 200 MHz (DS43 blink frequency rises with the faster clock)

4 - Change Clock Usage to ECC Modules

4 - All Being Clocked

With Full Performance, the PL power is about 1970mW

1.6.3 Partial Reconfiguration for Hardened Cores

The memory controllers contain ECC. Using these optimized designs can save power over a created design.

With Hard ECC, the PL power is about 1840mW

About 93% of the original power

3 - Change Clock Frequency to ECC Modules

2 - 50 MHz

If the full performance is not needed, the Dynamic Power can be scaled by reducing the Clock Frequency

In this case, it is done by changing the clock divider in the Programmable Logic

With Frequency Scaling to 50 MHz, the PL power is about 1120mW

About 57% of the original power

4 - Change Clock Usage to ECC Modules

2 - Quarter Being Clocked

This is one example of switching the design without overwriting it

In this case, only a portion of the circuit is being clocked

With Data Rate Switching to a Quarter Being Clocked, the PL power is about 994mW

About 50% of the original power

3 - Change Clock Frequency to ECC Modules

1 - 0 MHz

With No Clock, this should be Idle, drawing the static power of the device.

With the system Idle, the PL power is about 770mW

About 39% of the original power

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy