This page describes the steps for creating and building a 2019.1 PetaLinux project for use with the ZCU111 RFSoC Evaluation tool.

Table of Contents

Overview

The ZCU111 RFSoC Eval Tool has three designs based on the functionality. A detailed information about the three designs can be found from the following pages.

This tutorial includes the following:-

Steps to source and setup the petalinux tool for building the images.

Step-by-step tutorial to build all the images using the petalinux tool.

Information about the relevant kernel and device tree patches as well as the applications within the designs.

For more details on ZU+ RFSoC RF Data Converter Evaluation Tool refer to ZCU111 RFSoC RF Data Converter Evaluation Tool Getting Started Guide.

Building the Linux Image

Installation

PetaLinux consists of three key elements: pre-configured binary bootable images, fully customizable Linux for the Xilinx device, and PetaLinux SDK which includes tools and utilities to automate complex tasks across configuration, build, and deployment.Visit the PetaLinux wiki page for more details. Refer to the PetaLinux Tool Documentation (UG1144) for installation.

Procedure to build the Linux Image

The following section provides the steps to build all the images using the petalinux tool.

Set $DCET_HOME environment variable as given below.

% export DCET_HOME=</path/to/download/zipfile>/rdf0476-zcu111-RFdc-eval-tool-2019.1

1. Sourcing the petalinux tool:

% source <path/to/petalinux-installer>/petalinux-v2019.1/petalinux-v2019.1-final/settings.sh

2. Post petalinux installation, $PETALINUX variable should be set, command to cross-check the variable:

% echo $PETALINUX

3. Create project from .bsp file:

% cd $DCET_HOME/apu/ % petalinux-create -t project -s rfsoc_petalinux_bsp.bsp % cd rfsoc_petalinux_bsp

a. After creating project, please refer to Petalinux Build Tutorial for ZU+ RFSoC ZCU111 2019.1 and 2019.2#Modifications on top of 2019.1 released BSP section, for detailed information on changes in this TRD on top of released 2019.1 petalinux BSP.

b. As per the TRD flow, by-default NON-MTS bitstream and device-tree are loaded first and thereafter the requested bitstream and respective device-tree. Hence, when building any other design, NON-MTS binaries should always be generated first and kept in SD-Card. Otherwise, it will throw an error.

4. Configure the PetaLinux project using step “a” or “b”.

a) With the pre-built hdf located in folder <pl/<design_path>pre-built/rfsoc_trd>, depending on the design, user can select the "path".

Make sure the design_path indicates the folder in which the hdf resides.

% petalinux-config --get-hw-description=$DCET_HOME/pl/<design_path>/pre-built/rfsoc_trd/

For Example : If the user wants to build for Non-MTS Design, the design_path would be given as below:

% petalinux-config --get-hw-description=$DCET_HOME/pl/NON-MTSDesign_8x8/project/zcu111_rfsoc_trd.sdk/

b) If Vivado project is modified/design is changed, user is expected to configure the bsp with the modified hdf file as follows:

% petalinux-config --get-hw-description=$DCET_HOME/pl/<design_path>/project/zcu111_rfsoc_trd.sdk/

After executing step "a" or "b", petalinux menuconfig will be displayed, change the following:

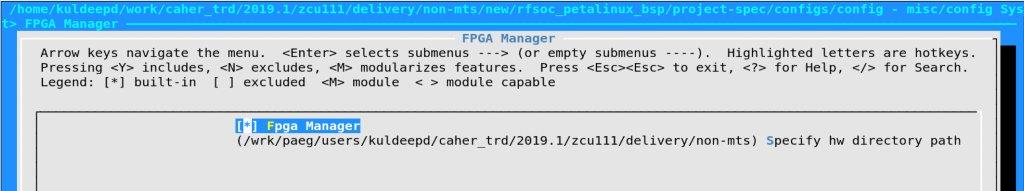

In FPGA Manager:

i. Enable "FPGA Manager".

ii. In "Specify hw directory path", add path to hdf as $DCET_HOME/pl/<design_path>pre-built/rfsoc_trd/.

iii. Save and Exit.

5. Build all Linux image components along with Evaluation Tool application:

% petalinux-build

6. Build device-tree for respective designs as follows:

% cd pre-built/linux/images/

This step is required as we load the design-type bitstream and design-type device-tree dynamically by enabling the FPGA-manager. Therefore, pl.dtsi is not part of packaged kernel image (image.ub) and has to be compiled and loaded separately.

a. For SSR IP:

% ./dtc -O dtb -o pl.dtbo -b 0 -@ pl_ssr.dtsi

b. For MTS:

% ./dtc -O dtb -o pl.dtbo -b 0 -@ pl_mts.dtsi

c. For Non-MTS:

% ./dtc -O dtb -o pl.dtbo -b 0 -@ pl_nonmts.dtsi

d. For custom device-tree, it should be generated and then modified by taking reference from the shared design-type (mts/non-mts/ssr) device-trees, copied to this same directory and compiled as below:

% ./dtc -O dtb -o pl.dtbo -b 0 -@ <custom-name>.dtsi

7. Create <design_type> sub-directories in the sd-card directory:

% mkdir -p $DCET_HOME/sd-card/mts % mkdir -p $DCET_HOME/sd-card/nonmts % mkdir -p $DCET_HOME/sd-card/ssr

8. Copy pl.dtbo to sdcard directory. This step should be executed for each design.

% cp pl.dtbo $DCET_HOME/sd-card/<design_type>

9. Generate bitstream in bin format. This step should be executed for each design.

% bootgen -image bitstream.bif -arch zynqmp -o zcu111_rfsoc_trd_wrapper.bit.bin -w

10. Copy bitstream to sdcard directory. This step should be executed for each design.

% cp zcu111_rfsoc_trd_wrapper.bit.bin $DCET_HOME/sd-card/<design_type>

11. Create a boot image (BOOT.BIN) including FSBL, ATF, PMUFW and u-boot:

% cd $DCET_HOME/apu/rfsoc_petalinux_bsp/images/linux % petalinux-package --force --boot --fsbl zynqmp_fsbl.elf --pmufw pmufw.elf --u-boot u-boot.elf

12. Copy the BOOT.bin and image.ub to the sdcard:

% cp BOOT.BIN image.ub $DCET_HOME/sd-card

Modifications on top of 2019.1 released BSP

Below are the modification in this TRD for linux-kernel, rfdc drivers, rftool and rfdc example application, on top of 2019.1 petalinux released BSP. For more details on patch information please refer to https://www.xilinx.com/support/answers/72405.html.

- Kernel patch information as follows:

% vim project-spec/meta-user/recipes-kernel/linux/linux-xlnx_%.bbappend

SRC_URI_append = " \

file://0001-power-supply-irps-Add-support-for-irps-supply.patch \

file://0002-drivers-misc-add-support-for-DDR-memory-management.patch \

file://0003-dmaengine-xilinx_dma-In-SG-cyclic-mode-allow-multipl.patch \

file://0004-drivers-misc-add-support-for-selecting-mem-type.patch \

file://0005-i2c-cadence-Implement-timeout.patch \

file://0006-i2c-muxes-update-Mux-register-always.patch \

file://0007-drivers-misc-change-ADC-packet-size-as-per-FIFO-size.patch \

file://0008-drivers-misc-change-parameters-for-of_dma_configure.patch \

file://0009-plmem-clean-up-sysfs-node-and-character-device-nodes.patch \

file://0010-dma-clean-the-BD-s-only-when-done-bit-is-set.patch \

"

- RFDC driver patch information as follows:

% vim project-spec/meta-user/recipes-bsp/rfdc/rfdc_%.bbappend

SRC_URI_append = " \

file://0001-rfdc-add-support-to-turn-off-mixer.patch \

"

- RFTOOL application patch as follows:

% vim project-spec/meta-user/recipes-apps/rftool/rftool.bb

- RFDC example application patch as follows:

% vim project-spec/meta-user/recipes-apps/rfdc-data-write-example/rfdc-data-write-example.bb

- RFDC Self-test application changes as follows:

% vim project-spec/meta-user/recipes-bsp/rfdc-examples/rfdc-selftest_%.bbappend

SRC_URI_append = " \

file://0001-selftest_example-change-default-frequency.patch \

"

To get "project-spec/meta-user/" folder, please extract files from. bsp using step #3 from section Petalinux Build Tutorial for ZU+ RFSoC ZCU111 2019.1 and 2019.2.

Once the images are built successfully the user can refer to ZCU111 RFSoC RF Data Converter Evaluation Tool Getting Started Guide for further information on test