The purpose of this page is to describe the Linux DRM driver for the Xilinx DisplayPort 1.4 Tx Subsystem Soft IP for the Zynq UltraScale+ MPSoC.

...

The purpose of this page is to describe the Linux DRM driver for Xilinx DisplayPort 1.4 TX Subsystem Soft IP for Zynq Ultrascale+ MPSoC.

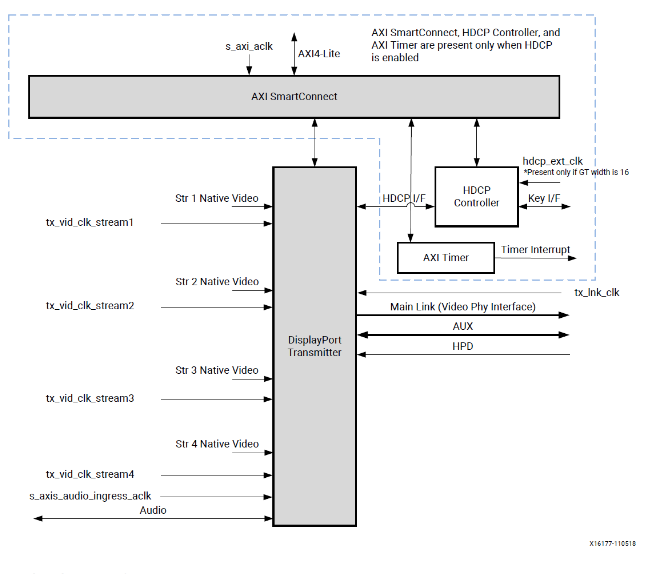

The DisplayPort 1.4 Tx Subsystem implements functionality of a video source as defined by the Video Electronics Standards Association (VESA)'s DisplayPort standard v1.4 and supports driving resolutions of up to Full Ultra HD (FUHD) at 30 fps. The subsystem is a hierarchical IP that bundles a collection of DP TX-related IP sub-cores and outputs them as a single IP. The subsystem takes incoming video stream and transfers them to an DP stream. The stream is then forwarded to the video PHY layer. Below is the block diagram of DisplayPort 1.4 Tx Subsystem.

Figure 1. Block diagram of DisplayPort 1.4 Tx Subsystem

The DP 1.4 Tx Subsystem is a MAC subsystem which works with a Video PHY Controller (PHY) to create a video connectivity system. The DP 1.4 Tx Subsystem is tightly coupled with the Xilinx Video PHY Controller, which itself is independent and offer flexible architecture with multiple-protocol support. Both MAC and PHY are dynamically programmable through the AXI4-Lite interface.

Figure 2. Block diagram of MAC Interface with PHY

Driver Overview

DP Tx is the last node in the display pipeline. The Linux driver is implemented as a sub-component of the Xilinx DRM KMS bridge driver (bridge driver name : xlnx) and implements the encoder/connector interface. The subsystem includes the video timing generator and Tx sub-core. Driver implements the DRM callbacks to read the display EDID and present it to the framework anytime a display is connected. It works in tandem with the DRM bridge driver to validates each mode listed in the EDID and reject unsupported modes.

On mode change request from user application driver works in conjunction with DRM framework to validate the requested mode to ensure the stream can be generated by Tx core and is supported by the attached display. If requested mode is supported, the driver will configure Tx sub-core for new mode ,the internal video timing controller (VTC) to generate requisite video timing for it .It also configures the PHY layer for the new mode and manages all required interaction between MAC & PHY layer.

After mode setup is complete PHY state machine is reset and put into a wait state awaiting the reference clock for the new mode from an external clock source. DRM framework requests the registered clock producer to generate the clock for desired mode.

IP/Driver Features

| IP Feature | 2020.1 | 2020.2 | 2021.1 |

| IP Version Supported | 2.1 | 3.0 | 3.0 |

| Supports AXI4-Stream, native video input interfaces | Axi-Stream Video Only | Axi-Stream Video Only | Axi-Stream Video Only |

| Support for 2 pixel per sample | Yes | Yes | Yes |

Support color space for RGB, YUV 4:4:4, YUV 4:2:2,Y-only | Yes | Yes | Yes |

| Audio support for 2 to 8 channelst | Yes | Yes | Yes |

| 8, 10, 12, and 16-bit Deep-color support | 8 and 10-bit only | 8 and 10-bit only | 8 and 10-bit only |

| Support for 16-bit GT width. | Yes | Yes | Yes |

| Support HDCP 2.x | No | No | No |

| HDCP in MST mode | No | No | No |

| In-band stereo | No | No | No |

| Video AXI4-Stream interface is not scalable with dynamic pixel mode selection | No | No | No |

| Dual-pixel splitter in native video mode | No | No | No |

| Supported resolution up to 8k30 | Yes | Yes | Yes |

| Supported interlaced mode | No | No | No |

Missing Features / Known Issues / Limitations in Driver

- This driver does't support following features

- HDCP

Kernel Configuration Options for Driver

2019.2 and onwards: Supports ONLY the new Xilinx DRM framework driver and PL crtc and can be enabled via following configurations options CONFIG_DRM_XLNX and CONFIG_DRM_XLNX_PL_DISP

The above defined options will only enable the new DRM framework.

2021.1 and onwards DisplayPort Tx driver is built as a part of the kernel. Hence enable the DisplayPort Tx driver in the kernel configuration. Run the below command from the petalinux project and select "Xilinx DRM DisplayPort Subsystem Driver".

Code Block theme Midnight $petalinux-config -c kernel

- 2021.1 and onwards Video phy controller driver is built as out-of-tree kernel module and therefore required no kernel configuration. However to enable the drive user must include it in the rootfs. Following steps are required to enable the driver.

- Make sure the meta-user layer has the recipe-dp included.

Add the recipe to petalinux image. Edit project-spec/meta-user/conf/user-rootfsconfig and add the new recipe at the end

Code Block theme Midnight CONFIG-kernel-module-dp

Next include the driver in the rootfs

Code Block theme Midnight $petalinux-config -c rootfs

- Select "user-pakages->modules->kernel-module-dp", save and exit

Build the project

Code Block theme Midnight

Building Driver Modules

Note: Below steps are applicable for building images for 2020.1

- Create a directory to build driver modules in local machine.

- example : mkdir build_dir

- clone the linux-xlnx from git https://github.com/Xilinx/linux-xlnx.git to build_dir.

- cd build_dir

- git clone https://github.com/Xilinx/linux-xlnx.git

- Clone the dp-modules to build_dir directory

- git clone https://github.com/Xilinx/dp-modules.git

- create a directory for the kernel output

- mkdir kernel_output

Create a make file and copy the below contents to that

| Code Block | ||

|---|---|---|

| ||

export TOP_DIR = $(shell pwd)

BOARD_NAME := zcu102

export ARCH = arm64

GCC_PREFIX = <cross-compiler path>

export DP_SOURCE := $(TOP_DIR)/dp-modules

export KERNEL_SOURCE := $(TOP_DIR)/linux-xlnx

export OUTPUT_DIR := $(TOP_DIR)/output

export KERNEL_OUTPUT := $(OUTPUT_DIR)/linux-xlnx-$(ARCH)

kernel:

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -C $(KERNEL_SOURCE) xilinx_zynqmp_defconfig O=$(KERNEL_OUTPUT)

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) O=$(KERNEL_OUTPUT) Image

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) O=$(KERNEL_OUTPUT) modules

modules:

ARCH=$(ARCH) CROSS_COMPILE=$(GCC_PREFIX) make -j 40 -C $(KERNEL_SOURCE) M=$(DP_SOURCE) O=$(KERNEL_OUTPUT) modules

find $(DP_SOURCE) -type f -name '*.o' -delete

find $(DP_SOURCE) -type f -name '*.cmd' -delete

find $(DP_SOURCE) -type f -name 'Modules' -delete

find $(DP_SOURCE) -type f -name 'Module.*' -delete

find $(DP_SOURCE) -type f -name '*.order' -delete

find $(DP_SOURCE) -type f -name '*.mod.c' -delete

find $(DP_SOURCE) -type f -name '*.mod' -delete |

run the below command to build the kernel

- $ make kernel

- run the below command to build the dp-modules

- $make modules

- Now the DP Tx driver is ready to use.

Device Tree Binding

The dts node should be defined with correct hardware configuration. An example device tree node is documented in

2020.1: Documentation/devicetree/bindings/xlnx,v-dp-tx-ss.txt

2020.2: Documentation/devicetree/bindings/xlnx,dp-tx.yaml

2021.1 : Documentation/devicetree/bindings/display/xlnx/xlnx,dp-tx.yaml

Example Design Architecture

Figure 3. DisplayPort Tx example design architecture

Test Procedure

DP-Tx can be manually configured to generate the required mode. An open source utility like modetest can be used to configure the display pipeline.

DDR ==>FB_Rd (DMA)==>DP _Tx

2020.1 and on wards Sample command to set a mode is shown below

| Code Block | ||

|---|---|---|

| ||

%> modetest -M xlnx -s <connector_id>[@<crtc_id>]:<mode>[-<vrefresh>][@<format> |

example command

| Code Block | ||

|---|---|---|

| ||

%> modetest -M xlnx -s 35:1920x1080-60@BG24 |

Above command will generate a color bar pattern at requested resolution in DDR, configures the DMA to read the frame from DDR and configures the DP Tx for said resolution. As a final result Color Bar at defined resolution should be visible on screen.

Driver also supports changing output color formats dynamically. Available output color formats supported by DMA engine can be determined using modetest utility as shown below

| Code Block | ||||

|---|---|---|---|---|

| ||||

root@xilinx-zcu102-2021_1:/media# modetest -M xlnx

Encoders:

id crtc type possible crtcs possible clones

34 0 TMDS 0x00000001 0x00000000

Connectors:

id encoder status name size (mm) modes encoders

35 0 connected DP-1 700x390 39 34

modes:

name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

7680x4320 29.93 7680 7710 7720 7880 4320 4323 4328 4368 1030240 flags: phsync, nvsync; type: preferred, driver

7680x4320 24.00 7680 7728 7760 7880 4320 4323 4328 4369 826250 flags: phsync, nvsync; type: preferred, driver

3840x2160 60.00 3840 3888 3920 4000 2160 2163 2168 2222 533250 flags: phsync, nvsync; type: preferred, driver

3840x4320 60.00 3840 3888 3920 4040 4320 4323 4333 4368 1058790 flags: phsync, nvsync; type: driver

3840x4320 48.00 3840 3888 3920 4040 4320 4323 4333 4418 856720 flags: phsync, nvsync; type: driver

3840x2160 29.98 3840 3888 3920 4000 2160 2163 2168 2191 262750 flags: phsync, nvsync; type: driver

2560x1440 59.95 2560 2608 2640 2720 1440 1443 1448 1481 241500 flags: phsync, nvsync; type: driver

1920x1200 59.88 1920 2056 2256 2592 1200 1203 1209 1245 193250 flags: nhsync, pvsync; type: driver

2048x1080 59.99 2048 2096 2128 2208 1080 1083 1093 1111 147160 flags: phsync, nvsync; type: driver

2048x1080 23.90 2048 2096 2128 2208 1080 1083 1093 1099 58000 flags: phsync, nvsync; type: driver

1920x1080 60.00 1920 2008 2052 2200 1080 1084 1089 1125 148500 flags: nhsync, nvsync; type: driver

1920x1080 60.00 1920 2008 2052 2200 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

1920x1080 59.94 1920 2008 2052 2200 1080 1084 1089 1125 148352 flags: phsync, pvsync; type: driver

1920x1080 50.00 1920 2448 2492 2640 1080 1084 1089 1125 148500 flags: phsync, pvsync; type: driver

1920x1080 24.00 1920 2558 2602 2750 1080 1084 1089 1125 74250 flags: phsync, pvsync; type: driver

1920x1080 23.98 1920 2558 2602 2750 1080 1084 1089 1125 74176 flags: phsync, pvsync; type: driver

1600x1200 60.00 1600 1664 1856 2160 1200 1201 1204 1250 162000 flags: phsync, pvsync; type: driver

1680x1050 59.95 1680 1784 1960 2240 1050 1053 1059 1089 146250 flags: nhsync, pvsync; type: driver

1280x1024 75.02 1280 1296 1440 1688 1024 1025 1028 1066 135000 flags: phsync, pvsync; type: driver

1280x1024 60.02 1280 1328 1440 1688 1024 1025 1028 1066 108000 flags: phsync, pvsync; type: driver

1280x800 59.81 1280 1352 1480 1680 800 803 809 831 83500 flags: nhsync, pvsync; type: driver

1280x720 60.00 1280 1390 1430 1650 720 725 730 750 74250 flags: phsync, pvsync; type: driver

1280x720 59.94 1280 1390 1430 1650 720 725 730 750 74176 flags: phsync, pvsync; type: driver

1280x720 50.00 1280 1720 1760 1980 720 725 730 750 74250 flags: phsync, pvsync; type: driver

1024x768 75.03 1024 1040 1136 1312 768 769 772 800 78750 flags: phsync, pvsync; type: driver

1024x768 60.00 1024 1048 1184 1344 768 771 777 806 65000 flags: nhsync, nvsync; type: driver

800x600 75.00 800 816 896 1056 600 601 604 625 49500 flags: phsync, pvsync; type: driver

800x600 60.32 800 840 968 1056 600 601 605 628 40000 flags: phsync, pvsync; type: driver

720x576 50.00 720 732 796 864 576 581 586 625 27000 flags: nhsync, nvsync; type: driver

720x576 50.00 720 732 796 864 576 581 586 625 27000 flags: nhsync, nvsync; type: driver

720x480 60.00 720 736 798 858 480 489 495 525 27027 flags: nhsync, nvsync; type: driver

720x480 60.00 720 736 798 858 480 489 495 525 27027 flags: nhsync, nvsync; type: driver

720x480 59.94 720 736 798 858 480 489 495 525 27000 flags: nhsync, nvsync; type: driver

720x480 59.94 720 736 798 858 480 489 495 525 27000 flags: nhsync, nvsync; type: driver

640x480 75.00 640 656 720 840 480 481 484 500 31500 flags: nhsync, nvsync; type: driver

640x480 60.00 640 656 752 800 480 490 492 525 25200 flags: nhsync, nvsync; type: driver

640x480 59.94 640 656 752 800 480 490 492 525 25175 flags: nhsync, nvsync; type: driver

640x480 59.94 640 656 752 800 480 490 492 525 25175 flags: nhsync, nvsync; type: driver

720x400 70.08 720 738 846 900 400 412 414 449 28320 flags: nhsync, pvsync; type: driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

00ffffffffffff0010ac47414c353730

201b0104b54627783a7645ae5133ba26

0d5054a54b008100b300d100a9408180

d1c0010101014dd000a0f0703e803020

3500ba892100001a000000ff0046464e

584d3738373037354c0a000000fc0044

454c4c205550333231384b0a000000fd

00184b1eb46c010a2020202020200270

02031df150101f200514041312110302

161507060123091f0783010000a36600

a0f0701f8030203500ba892100001a56

5e00a0a0a0295030203500ba89210000

1a7c3900a080381f4030203a00ba8921

00001aa81600a08038134030203a00ba

892100001a0000000000000000000000

00000000000000000000000000000047

701279000012001682100000ff0edf10

000000000044454c47414c3537300301

5070920184ff1dc7001d800900df102f

0002000400c1420184ff1dc7002f801f

00df10300002000400a84e0104ff0ec7

002f801f00df10610002000900979d01

04ff0ec7002f801f00df102f00020009

00000000000000000000000000009890

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 3

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

313a313a323a313a303a303a33383430

3a3433323000

21 CRTC_ID:

flags: object

value: 0

36 sync:

flags: range

values: 0 1

value: 0

37 bpc:

flags: enum

enums: 6BPC=6 8BPC=8 10BPC=10 12BPC=12

value: 8

CRTCs:

id fb pos size

33 0 (0,0) (0x0)

nan 0 0 0 0 0 0 0 0 0 flags: ; type:

props:

23 ACTIVE:

flags: range

values: 0 1

value: 0

24 MODE_ID:

flags: blob

blobs:

value:

20 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

25 VRR_ENABLED:

flags: range

values: 0 1

value: 0

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

32 0 0 0,0 0,0 0 0x00000001

formats: XB30 VU24 XV30 YUYV XV20 BG24

props:

9 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

18 FB_ID:

flags: object

value: 0

19 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

21 CRTC_ID:

flags: object

value: 0

14 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

16 CRTC_W:

flags: range

values: 0 2147483647

value: 1920

17 CRTC_H:

flags: range

values: 0 2147483647

value: 1080

10 SRC_X:

flags: range

values: 0 4294967295

value: 0

11 SRC_Y:

flags: range

values: 0 4294967295

value: 0

12 SRC_W:

flags: range

values: 0 4294967295

value: 125829120

13 SRC_H:

flags: range

values: 0 4294967295

value: 70778880

Frame buffers:

id size pitch

root@xilinx-zcu102-2021_1:/media# |

Refer Line "formats"that indicates the FrameBuffer DMA IP configuration supports XB30 VU24 XV30 YUYV XV20 BG24 GREY Y10 color formats. This setting is configured by the DMA driver device tree node property xlnx,vid-formats

Debug Capability

DP Linux driver implements the capability to tap IP status at pre-defined points in the control flow. User can enable the debug taps by uncommenting the pre-processor directive (#define DEBUG) to monitor the progress within the driver. All debug prints are sent to serial console and can be viewed in kernel dmesg buffer

Boards Supported

Driver has been tested on following boards

- zcu102 Rev-D

- zcu102 Rev 1.0

Change Log

- 2020

2021.

21