Zynq UltraScale+ MPSoC VCU TRD 2018.3 - SDI Video Display

...

Table of Contents

| Table of Contents | ||

|---|---|---|

|

1 Overview

The primary goal of this Design is to demonstrate the capabilities of VCU hard block present in Zynq UltraScale+ EV devices. The TRD will serve as a platform to tune the performance parameters of VCU and arrive at optimal configurations for encoder and decoder blocks with the streaming use case where bandwidth plays a vital role.

This design supports the following video interfaces:

Sources:- File source (SD card, USB storage, SATA hard disk).

- Stream-In from network or internet.

Sinks:

- SDI-Tx display pipeline implemented in the PL.

VCU Codec:

- Video Encode/Decode capability using VCU hard block in PL

- AVC/HEVC encoding.

- Encoder/decoder parameter configuration.

Streaming Interfaces:

- 1G Ethernet on PS

Supported Features:

The table below provides the supported encoder feature in this release.

Resolution Command Line Single Stream Multi-stream 4kp60 √ NA 4kp30 √ NA 1080p60 √ NA

√ - Supported

NA – Not applicable

x – Not supportedDeliverables:

Pipeline Input source

Output Type

Resolution

Video encode/Decoder type

Deliverables

Playback pipeline

File Source/ Stream-In

SDI-Tx

4K/1080p

HEVC/AVC

Playback of the local-file/stream-in with video decoded using VCU and display on SDI-Tx.

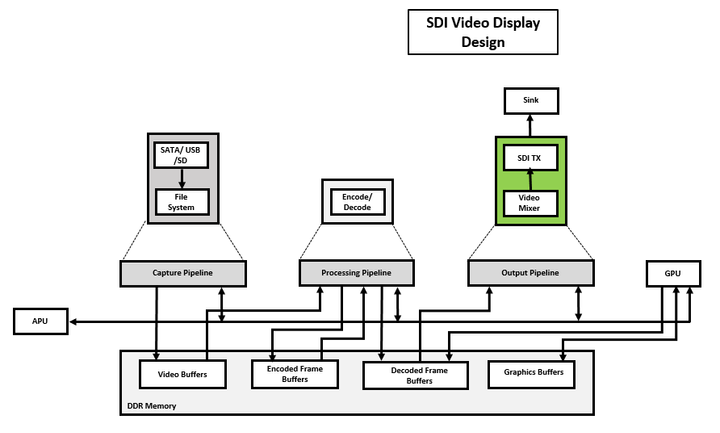

The below figure shows the SDI Video Display design hardware block diagram.

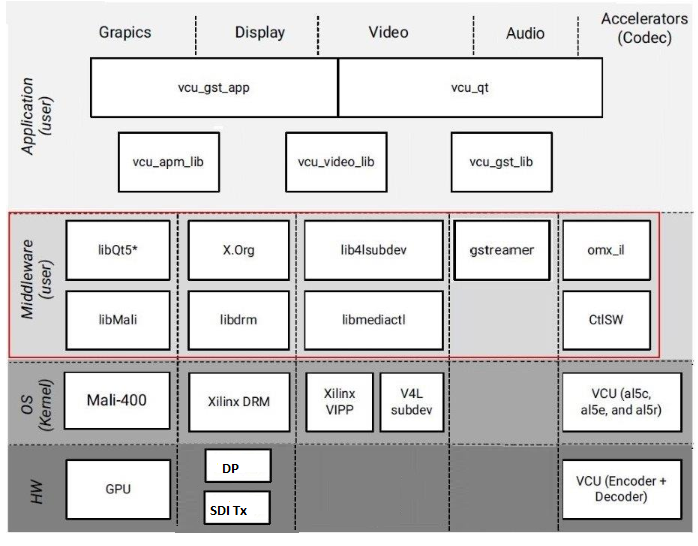

The below figure shows the SDI Video Display design software block diagram.

1.1 Board Setup

Refer below link for Board Setup

...