Table of Contents

| Table of Contents | ||

|---|---|---|

|

Introduction

The Xilinx UHD SDI Rx Subsystem consists of UHD SDI Rx IP core, an SDI to native video bridge followed by a Native to AXI-4 S bridge. It is capable of detecting the SD, HD, 3GA, 3GB, 6G and 12G (upto 8 data streams) type SDI streams. The maximum resolution it supports is 4096x2160p60 in 12G mode. The SDI Rx IP allows the configuration of the modes to be detected at run time or a fixed mode. It also allows the Framer to be enabled. A video lock event is generated when the incoming SDI mode and transport stream is detected and is stable for a configurable number of video clocks as programmed in the Video Lockout Window. When the input video stream is stopped or the type changed, a video unlock event is generated. The IP gives out the CRC and EDH error status. When the bridges are enabled, then the AXI-4 Stream of YUV 422 10 bit per component and 2 pixels per clock is sent out.The SDI Rx Subsystem driver (xilinx-sdirxss.c) is based on the V4L2 framework.

It creates a subdev node(/dev/v4l-subdev*) which can be used to query and configure the UHD SDI Rx Subsystem IP.

The SDI Rx IP would be the first node in the video capture pipeline.

It exposes various V4L controls which can be used to configure the subsystem like auto detection of SDI modes, Framer enable, etc and query the status like CRC status, EDH errors, etc.

It also exposes certain V4L events like video unlock, bridge overflow/underflow, video source change, etc which can be used by application to trigger certain actions.

The general description of V4L2 framework is documented here, v4l2-framework.txt.

IP/Driver Features

| IP feature | 2018.1 on wards | 2019.2 | 2020.1 | 2020.2 | 2021.1 |

|---|---|---|---|---|---|

| IP version | 2.0 | ||||

| Supports AXI4-Stream, native video and native SDI user interfaces | Supports only AXI4-Stream output interface | ||||

| Support for 2 pixel per sample | Yes | ||||

| 10-bit per color component | Yes | Added support for 12 bit | |||

| Supports YUV 4:2:2 and YUV 4:2:0 color space | Yes | Added support for YUV444 in IP. Driver doesn't support | Supports YUV 420 / 422 / 444 and RGB | ||

| HFR (High Frame Rate) Support 96/1.001, 96, 100, 120/1.001 and 120 Hz | NA | Not supported in driver | SupporteSupported | ||

| AXI4-Lite interface for register access to configure different subsystem options | Yes | ||||

| Audio support | Separate driver | ||||

Standards compliance

| Yes* | ||||

| HLG support | N.A | Supported | |||

Other driver features supported are -

- Detect SD, HD, 3GA/3GB, 6G, 12G (upto 8 Data Streams)

- Auto detect multiple modes OR Fixed Mode detection

- Framer enable/disable

- Programmable Video Lock Window

- EDH & CRC error counters

- Video Lock, Unlock, Bridge Over/UnderFlow interrupts

- Separate bits to control SDI to Native and Native to AXI4-S bridge

- ST352 Payload

- Mode and Transport type detection

- Fractional / Integral Frame rate

- Interlaced / Progressive Transport

- Family detection

Missing Features / Known Issues / Limitations in Driver

- In case of a HD stream without payload, a progressive segmented frame (pSF) will be reported incorrectly as Interlaced as the driver relies on the IP's transport scan locked bit.

- *Multiple instances capability not tested

- *Tested with only 12G 8DS configuration

- HD 1280x720p24 and HD 1280x720p23.98 - Incorrect colors are captured

- In some 3GB 1080 modes, the colors in color bars are swapped.

- Tested with Phabrix SDI generator and Omnitek Ultra4K

- Doesn't support to YUV444 in 2019.2

Kernel Configuration

CONFIG_VIDEO_XILINX_SDIRXSS and CONFIG_VIDEO_XILINX should be enabled.Device Tree Binding

The dts node should be defined with correct hardware configuration. How to define the node is documented in xlnx,sdirxss.txtTest Procedure

Certain parameters like Framer enable, Video lockout window, etc can be configured using the YAVTA tool as follows -

For example, to list all the controls and current values

| Code Block | ||

|---|---|---|

| ||

yavta -l /dev/v4l-subdev0 #Below is sample output when video is not locked and not streaming root@zcu106-zynqmp:~# yavta -l /dev/v4l-subdev0 Device /dev/v4l-subdev0 opened. --- User Controls (class 0x00980001) --- control 0x0098ca01 `SDI Rx : Enable Framer' min 0 max 1 step 1 default 1 current 1. control 0x0098ca02 `SDI Rx : Video Lock Window' min 0 max -1 step 1 default 12288 current 12288. control 0x0098ca03 `SDI Rx : EDH Error Count Enable' min 0 max 65535 step 0 default 0 current 0. control 0x0098ca04 `SDI Rx : Modes search Mask' min 0 max 63 step 0 default 63 current 63. unable to get control 0x0098ca05: Invalid argument (22). control 0x0098ca05 `SDI Rx : Mode Detect Status' min 0 max 5 step 1 default 0 current n/a. control 0x0098ca06 `SDI Rx : CRC Error status' min 0 max -1 step 1 default 0 current 0. unable to get control 0x0098ca07: Invalid argument (22). control 0x0098ca07 `SDI Rx : EDH Error Count' min 0 max 65535 step 1 default 0 current n/a. unable to get control 0x0098ca08: Invalid argument (22). control 0x0098ca08 `SDI Rx : EDH Status' min 0 max -1 step 1 default 0 current n/a. unable to get control 0x0098ca09: Invalid argument (22). control 0x0098ca09 `SDI Rx : TS is Interlaced' min 0 max 1 step 1 default 0 current n/a. unable to get control 0x0098ca0a: Invalid argument (22). control 0x0098ca0a `SDI Rx : Active Streams' min 1 max 16 step 1 default 1 current n/a. unable to get control 0x0098ca0b: Invalid argument (22). control 0x0098ca0b `SDI Rx : Is 3GB' min 0 max 1 step 1 default 0 current n/a. 11 controls found. Unable to get format: Inappropriate ioctl for device (25). |

...

- The SDI source connected to SDI Rx port and should be running.

- The driver should have been loaded successfully during kernel bootup.

- Running media-ctl should show resolution.

E.g. “media-ctl –d /dev/media0 –p”

- Always check if the lock has occurred or not.

- If the lock is occurred, is the current mode (SD, HD, 3GA, 3GB, 6G, 12GI or 12GF) same as source?

- What is the ST352 payload in RX_ST352_DATA_DS1 register? Decode it to get resolution and size and color format.

- Refer to driver code how to decode.

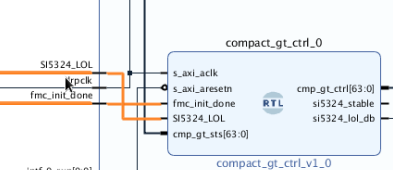

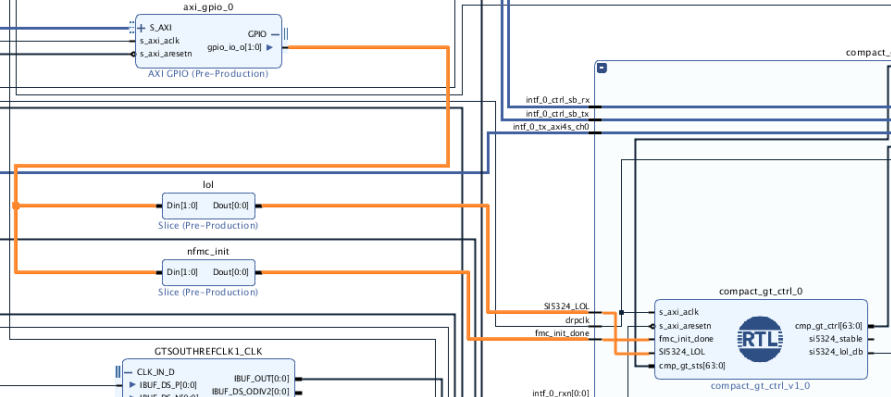

- Compact GT Reset - There are 2 signals connected to compact_gt which need to be toggled to have a clean reset of the GT.

The SI5324_LOL should be toggled to high and then made low. (Default low)

The fmc_init_done line should be toggled to low and then high (Default high).

FAQ

Q1 - While running yavta for resolution AxB with our source box, we see "Unable to start streaming: Invalid argument (22)." Why is this happening?

Ans - One possible reason is that the resolution that the SDI source is generating and what is being passed to yavta don't match.

Run media-ctl to find out the resolution currently being identified by the SDI Rx IP driver.

Read your SDI source documentation to know how to manipulate the resolutions.

Q2 - The frame rate reported by yavta is significantly lesser than expected.

Ans - Depending on your design and system load, there may be a case where there may be frame drops.

But double check the ST352 payload in SDI Rx to verify if the SDI source connected is correctly generating the required frame rate (fps).

You may have to refer to PG205 to decode the RX FAMILY to get the resolution and RX Frame Rate (in case of zero payload in 2017.3/4)

Family Detection

| rx_t_family | Transport Video Format | Active Pixels |

|---|---|---|

| 0000 | SMPTE ST 275 | 1920 x 1080 |

| 0001 | SMPTE ST 296 | 1280 x 720 |

| 0010 | SMPTE ST 2048-2 | 2048x1080 |

| 0011 | SMPTE ST 295 | 1920 x 1080 |

| 1000 | NTSC | 720 x 486 |

| 1001 | PAL | 720 x 576 |

| 1111 | Unknown | |

| Others | Reserved |

Frame Rate

| rx_t_rate | Frame Rate |

|---|---|

| 0000 | None |

| 0010 | 23.98 Hz |

| 0011 | 24 Hz |

| 0100 | 47.95 Hz |

| 0101 | 25 Hz |

| 0110 | 29.97 Hz |

| 0111 | 30 Hz |

| 1000 | 48 Hz |

| 1001 | 50 Hz |

| 1010 | 59.94 Hz |

| 1011 | 60 Hz |

| Others | Reserved |

Q3 - After boot up, even though there is valid SDI source connected, the IP is unable to detect the source and video is not locked. Why could this happen?

Ans - Check if the IP's registers are not default values after kernel boots up. E.g. MODULE_CTRL register should be 0x3F30. If the registers are in default state, it may mean the clocking to the IP is not correct. Please check device tree to set the correct clock source.

Boards Supported

Driver has been tested on the following boards- ZCU106 1.0

Known Issues

- AR68766 - SMPTE UHD-SDI RX Subsystem - Release Notes and Known Issues for the Vivado 2017.3 tool and later versions

Change log

2021.1

- Summary

- No change

2020.2

- Summary

- Add PICXO support

- Add support for Hybrid Log Gamma EOTF

- Add support for HFR

- Update the v4l2 format struct for quantization, xfer_func, colorimetryt, etc

- Fix Coverity warnings

- Commits

- v4l: xilinx: sdirxss: Add support for PICXO

- v4l: xilinx: sdirxss: Update video params when stream changes without

- v4l: xilinx: sdirxss: Fix colorimetry dectection for HD mode

- v4l: xilinx: sdirxss: Update HDR control type

- v4l: xilinx: sdirxss: Fix warnings for NULL_RETURNS

- v4l: xilinx: sdirxss: Fix warnings for CONSTANT_EXPRESSION_RESULT

- v4l: xilinx: sdirxss: Fix warnings for UNUSED_VALUE

2020.1

- Summary

- Add support for YUV 444/RBG in 10 bpc

- Add support for RBG/YUV444/YUV422/YUV420 in 12 bpc

- Support switching the GT clock in 12G mode from integer to fractional and vice versa

- Other fixes

- Commits

- v4l: xilinx: xsdirxss: Fix format height for interlaced and pSF mode

- v4l: xilinx: sdirxss: Add support for ST2081-10 Mode 2 in 6G mode

- v4l: xilinx: sdirxss: Add new 10/12 bit support

- v4l: xilinx: sdirxss: Add support for optional gt reset gpio

- v4l: xilinx: sdirxss: Fix IP reset on gt clock switch in 12G mode

- v4l: xilinx: sdirxss: Fix returning error on stream off

- v4l: xilinx: sdirxss: Add the missing timings

- v4l: xilinx: sdirxss: Add support to modify GT clock

- v4l: xilinx: sdirxss: Add YUV444 10 bpc support

2019.2

- Summary

- Fixed driver based on comments received while upstreaming like enumerating media bus formats.

- Fixed interrupt handling for combined lock/unlock interrupts and correctly clearing processed interrupts

- Commits

3de732f v4l: xilinx: sdirxss: Uninitialize the subsystem correctly

23b13a3 v4l: xilinx: sdirxss: Check for 10bpc in dt

df18806 v4l: xilinx: sdirxss: Call xsdirx_streamflow_control() directly

1df1d9f v4l: xilinx: sdirxss: Make functions static inline

75b9c47 v4l: xilinx: sdirxss: Fix code formatting and comments

4414443 v4l: xilinx: sdirxss: Correct handling of combined lock/unlock interrupts

784427f v4l: xilinx: sdirxss: Clear processed interrupts only

1c98050 v4l: xilinx: sdirxss: Add support to enumerate media bus formats

b1b4c50 v4l: xilinx: sdirxss: Replace single element array with variable

f3bd12b v4l: xilinx: sdirxss: Use clk_bulk_* apis

b996133 v4l: xilinx: sdirxss: Make structures constant

...