Table Contents

| Table of Contents |

|---|

...

To enable pin-controller driver in the kernel, the following configuration options need to be enabled:

| Code Block | ||

|---|---|---|

| ||

CONFIG_PINCTRL=y CONFIG_PINCTRL_ZYNQMP=y CONFIG_ARCH_ZYNQMP=y CONFIG_PINMUX=y CONFIG_GENERIC_PINCONF=y |

Devicetree (for 2018.1 release)

| Code Block | ||

|---|---|---|

| ||

pinctrl0: pinctrl {

compatible = "xlnx,zynqmp-pinctrl";

status = "disabled";

pinctrl_uart1_default: uart1-default {

mux {

groups = "uart1_0_grp";

function = "uart1";

};

conf {

groups = "uart1_0_grp";

slew-rate = <SLEW_RATE_SLOW>;

io-standard = <IO_STANDARD_LVCMOS18>;

};

conf-rx {

pins = "MIO1";

bias-high-impedance;

};

conf-tx {

pins = "MIO0";

bias-disable;

};

};

}; |

Devicetree (for 2017.4 and earlier releases)

| Code Block | ||

|---|---|---|

| ||

pinctrl0: pinctrl@ff180000 {

compatible = "xlnx,pinctrl-zynqmp";

status = "disabled";

reg = <0x0 0xff180000 0x0 0x1000>;

pinctrl_uart1_default: uart1-default {

mux {

groups = "uart0_4_grp";

function = "uart0";

};

conf {

groups = "uart0_4_grp";

slew-rate = <SLEW_RATE_SLOW>;

io-standard = <IO_STANDARD_LVCMOS18>;

};

conf-rx {

pins = "MIO18";

bias-high-impedance;

};

conf-tx {

pins = "MIO19";

bias-disable;

schmitt-cmos = <PIN_INPUT_TYPE_CMOS>;

};

};

}; |

Test procedure

The drivers are tested on actual ZynqMP zcu-102 board. Kernel logs are used to validate the functionality of the drivers. For negative testing,errors are deliberately injected in the device tree blob’s pin control nodes and then the functionality of the peripheral is checked.

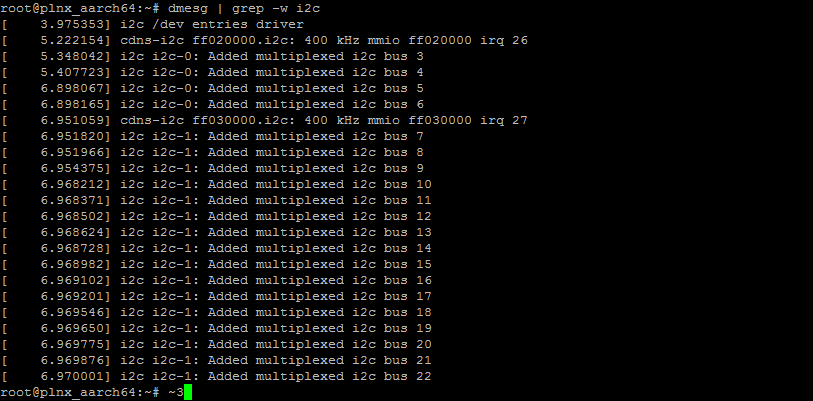

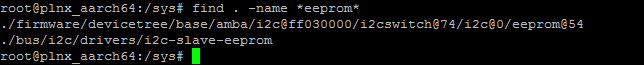

The testing observations (Kernel Logs) for I2C bus is mentioned hereafter. It can be seen from the kernel logs that under ideal scenario I2C is probed,

pins are properly configured, I2C bus entries are added and EEPROM is successfully attached over I2C, but under error scenarios pin control shouts for error,

no I2C busses are added as well as EEPROM node is not found.

Expected Output

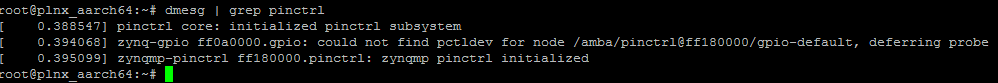

Ideal ScenarioSuccessfully Probed pin control drivers

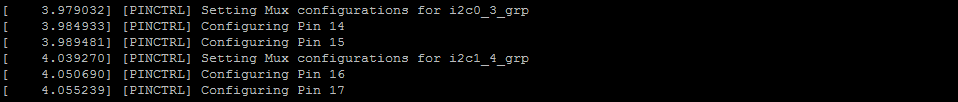

I2C pins configured via pin controller driver

I2C multiplexed busses added

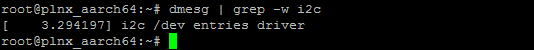

Error Scenario

In this case invalid I2C pin groups were provided and it can be seen that pin control driver shouts error

Also no multiplexed I2C busses were added

EEPROM also was not added over I2C interface

Mainline Status

This Driver is not available at Mainline.

Patches sent to mainline, review in progress.

Change Log

2017.1Summary:

- pinctrl: zynqmp: Add pin controller driver

- pinctrl: zynqmp: Resolved pin conflicts

- pinctrl: zynqmp: 1bit and 4bit data lane support for sdio

- pinctrl: zynqmp: Updated pmu pin groups

- pinctrl: zynqmp: Warning on IO Standard mismatch

- pinctrl: zynqmp: Updated error handling in config set

- pinctrl: zynqmp: Added support for drive strength configuration

- pinctrl: zynqmp: Reset pin config when it's freed

- pinctrl: zynqmp: Fix code and documentation warnings

- a95257b pinctrl: zynqmp: Add pin controller driver

- 5b41a9c pinctrl: zynqmp: Resolved pin conflicts

- 19be687 pinctrl: zynqmp: 1bit and 4bit data lane support for sdio

- 2bbdb44 pinctrl: zynqmp: Updated pmu pin groups

- 17aabf1 pinctrl: zynqmp: Warning on IO Standard mismatch

- fa365ff pinctrl: zynqmp: Updated error handling in config set

- bdc3cb5 pinctrl: zynqmp: Added support for drive strength configuration

- 089db66 pinctrl: zynqmp: Reset pin config when it's freed

- 322b2e7 pinctrl: zynqmp: Fix code and documentation warnings

2017.2

- None

2017.3

Summary:

- pinctrl: zynqmp: make it explicitly non-modular

- pinctrl: zynqmp: Remove additional space in DRIVE_STRENGTH

- zynqmp: Use new firmware.h instead of pm.h

- 99158ea pinctrl: zynqmp: make it explicitly non-modular

- 67fd56e pinctrl: zynqmp: Remove additional space in DRIVE_STRENGTH

- 5e81ba5 zynqmp: Use new firmware.h instead of pm.h

2017.4

- None.

2018.1

Summary:

- Add new pincontrol driver which fetches pin information from firmware than using hardcoded pins in driver

Commits:

- 5807afd pinctrl: zynqmp: Correct mismatch between driver and binding doc

- e0a388f drivers: pinctrl: Update ZynqMP pin control driver

- None.

2019.1

- None.

2019.2

Summary:

- drivers: Defer probe if firmware is not ready

Commits:

- 6a63448: drivers: Defer probe if firmware is not ready

2020.1

Summary:

- pinctrl: zynqmp: use module_platform_driver to simplify the code

Commits:

- 065cafc: pinctrl: zynqmp: use module_platform_driver to simplify the code

2020.2

Summary:

- Minor: Fix coverity warnings

Commits:

Related Links

...