Zynq UltraScale MPSoC VCU TRD 2019.1

...

| Table of Contents | ||

|---|---|---|

|

1 Revision History

This wiki page complements the 2019.1 a version of the MPSoC VCU TRD.

Change Log:

- Update all projects, IPs, and tools versions to 2019.1

- I2S capture and renderer Audio integrated into TRD

- Memory-based SCD support – Maximum 8 streams (7 HDMI, 1 MIPI)

- File-based PCIe transcode use case supported - host → device → host

- HDMI video capture and display with PL DDR

...

This is the main page of VCU TRD wiki, which has links to redirect wiki pages corresponding to individual design modules. It also explains the complete feature list and the supported resources of all the designs. TRD package weblink is provided for the user to download. This page also gives information on required software tools, IP licenses.

The Zynq® UltraScale+™ MPSoC Video Codec Unit (VCU) Targeted Reference Design (TRD) consists of an embedded video encoding/decoding application that runs on the Processing System (PS). The overall functionality of the TRD is partitioned between the Processing System (PS), Video Codec Unit, and Programmable Logic (PL) for optimal performance.

The primary goal of this TRD is to demonstrate the capabilities of the VCU core which is an integrated hard block present in Zynq UltraScale+ MPSoC EV devices. The TRD serves as a platform for the user to tune the performance parameters of VCU and arrives at an optimal configuration for encoder and decoder blocks for their specific use case. The TRD uses Vivado IP Integrator (IPI) flow for building the hardware design and Xilinx Yocto PetaLinux flow for software design. It uses Xilinx IPs and software drivers to demonstrate the capabilities of different components

The TRD supports the following video interfaces:

Sources (up-to 4K-60FPS):

...

Serial Communication:

- PCIe(Peripheral Component Interconnect Express)

Video format:

- NV12

- NV16

- XV15

- XV20

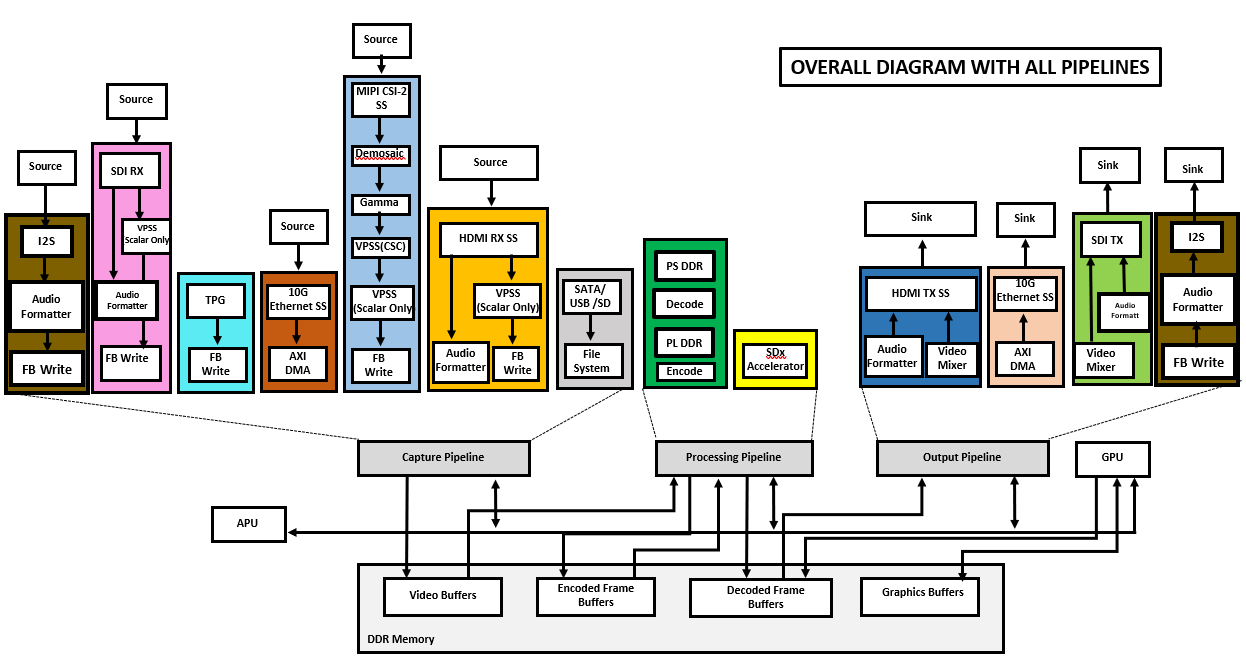

The below figure shows the TRD block diagram. It consists of all the Design Modules. The components of each design module are highlighted in unique colors in the diagram. The remaining blocks are common to all design modules as shown.

The VCU TRD 2019.1 the version consists of eleven design-modules as described below. Individual links below will redirect to the corresponding wiki pages and build and run the flow of individual designs modules.

...

- Linux host machine for all tool flow tutorials (see UG1144 for detailed OS requirements)

- PetaLinux Tools version 2019.1 (see UG1144 for installation instructions)

- VIVADO Design suite version 2019.1

- Git a distributed version control system

- Silicon Labs quad CP210x USB-to-UART bridge driver

- Serial terminal emulator e.g. teraterm

3.3 Download, Installation, and Licensing

...