Table of Contents

| Table of Contents | ||

|---|---|---|

|

Introduction

The AXI 10G/25G High Speed Ethernet Subsystem and USXGMII core are soft Xilinx IP core for use with the Xilinx Vivado® Design Suite. XXV Ethernet subsystem consists of a 10G/25G MAC including a 10BaseR PHY.

USXGMII Ethernet subsystem consists of a MAC similar to XXV For more information, please refer to the 10G/25G High Speed Ethernet Subsystem and UXSGMII product page which includes links to the official documentation and resource utilization.

Driver Sources

The source code for the driver is included with the Vitis Unified Software Platform installation, as well as being available in the Xilinx Github repository.

<If there are multiple drivers supporting this IP, we should make that statement here and add to the table>

| Driver Name | Path in Vitis | Path in Github |

|---|---|---|

| xxvethernet | <Vitis Install Directory>/data/embedded/XilinxProcessorIPLib/drivers/xxvethernet_<version> | https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/xxvethernet |

| Info |

|---|

Note: To view the sources for a particular release, use the rel-version tag in github. For example, for the 2020.1 release, the proper version of the code is: https://github.com/Xilinx/embeddedsw/tree/xilinx-v2020.1/XilinxProcessorIPLib/drivers/xxvethernet |

The driver source code is organized into different folders. The table below shows the xxvethernet driver source organization.

| Directory | Description |

|---|---|

| doc | Provides the API and data structure details |

| data | Driver .tcl and .mdd file |

| examples | Example applications that show how to use the driver features |

| src | Driver source files |

Driver Implementation

For a full list of features supported by these IP, please refer to the 10G/25G High Speed Ethernet Subsystem and UXSGMII product pages.

Features

The XXV Ethernet Standalone driver supports the following features: - 10G speed on xxvethernet MAC

- 1G/2.5G/5G/10G speeds on USXGMII MAC

- PHY management and GT management.

- Support for DMA interface

- Statistics gathering

- Optional support for jumbo frames up to 16 KB

Known Issues and Limitations

The following is a list of known limitations of the driver and features of the IP that are not currently implemented:

- Full checksum offload, VLAN, flow control and 1588 are not supported

Example Design Architecture

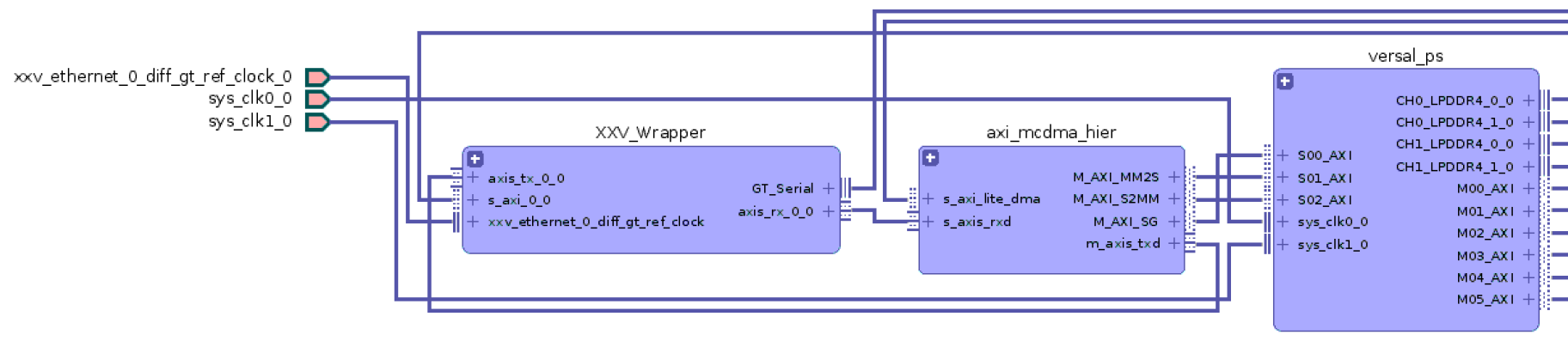

The examples that 10G/25G High Speed Ethernet Subsystem/USXGMII AXI4-Stream bus is connected to MCMDA DMA IP.

Example Applications

Refer to the driver examples directory for various example applications that exercise the different features of the driver. Each application is linked in the table below. The following sections describe the usage and expected output of the various applications. These example applications can be imported into the Vitis IDE from the Board Support Package settings tab.

Links to Examples

Examples Path: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/xxvethernet/examples

| Test Name | Example Source | Description |

|---|---|---|

| XXVEthernet mcdma example | xxxvethernet_example_intr_mcdma.c | This is an interrupt driven loopback example demonstrating a simple send-receive test case using XXVEthernet and MCDMA. This test loops through all 16 channels of the MCDMA connected to XXVEthernet MAC; an internal HW logic was used to direct RX packets to one of the 16 MCDMA channels using MAC address as the filter. User applications and design need to use their own logic if they intend to direct traffic to different RX channels deterministically. |

| USXGMII mcdma example | xxxvethernet_usxgmii_example_intr_mcdma.c | This is an interrupt driven loopback example demonstrating a simple send-receive test case using USXGMII and MCDMA. Since USXGMII has no internal loopback, this test needs to be done with and external loopback on the HW. The internal USXGMII phy is setup to enable auto-negotiation at 1G speed by default. This test loops through all 16 channels of the MCDMA connected to USXGMII MAC; an internal HW logic was used to direct RX packets to one of the 16 MCDMA channels using MAC address as the filter. User applications and design need to use their own logic if they intend to direct traffic to different RX channels deterministic-ally. |

Example Application Usage

XXVEthernet mcdma example

This is an interrupt driven loopback example demonstrating a simple send-receive test case using XXVEthernet and MCDMA.

Expected Output

| Code Block | ||

|---|---|---|

| ||

--- Enter main() --- This test may take several minutes to finish ChanId 1, MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xB0 ChanId 1 Single frame interrupt example passed ChanId 2, MacAddr: 0x0 0xF 0x53 0xE 0x9F 0xB0 ChanId 2 Single frame interrupt example passed ChanId 3, MacAddr: 0x0 0x10 0x53 0xE 0x9F 0xB0 ChanId 3 Single frame interrupt example passed ChanId 4, MacAddr: 0x0 0x18 0x53 0xE 0x9F 0xB0 ChanId 4 Single frame interrupt example passed ChanId 5, MacAddr: 0x0 0x20 0x53 0xE 0x9F 0xB0 ChanId 5 Single frame interrupt example passed ChanId 6, MacAddr: 0x0 0x28 0x53 0xE 0x9F 0xB0 ChanId 6 Single frame interrupt example passed ChanId 7, MacAddr: 0x0 0x30 0x53 0xE 0x9F 0xB0 ChanId 7 Single frame interrupt example passed ChanId 8, MacAddr: 0x0 0x38 0x53 0xE 0x9F 0xB0 ChanId 8 Single frame interrupt example passed ChanId 9, MacAddr: 0x0 0x40 0x53 0xE 0x9F 0xB0 ChanId 9 Single frame interrupt example passed ChanId 10, MacAddr: 0x0 0x48 0x53 0xE 0x9F 0xB0 ChanId 10 Single frame interrupt example passed ChanId 11, MacAddr: 0x0 0x50 0x53 0xE 0x9F 0xB0 ChanId 11 Single frame interrupt example passed ChanId 12, MacAddr: 0x0 0x58 0x53 0xE 0x9F 0xB0 ChanId 12 Single frame interrupt example passed ChanId 13, MacAddr: 0x0 0x60 0x53 0xE 0x9F 0xB0 ChanId 13 Single frame interrupt example passed ChanId 14, MacAddr: 0x0 0x68 0x53 0xE 0x9F 0xB0 ChanId 14 Single frame interrupt example passed ChanId 15, MacAddr: 0x0 0x70 0x53 0xE 0x9F 0xB0 ChanId 15 Single frame interrupt example passed ChanId 16, MacAddr: 0x0 0x78 0x53 0xE 0x9F 0xB0 ChanId 16 Single frame interrupt example passed Test passed --- Exiting main() --- |

USXGMII mcdma example

This is an interrupt driven loopback example demonstrating a simple send-receive test case using USXGMII and MCDMA.

Expected Output

| Code Block | ||

|---|---|---|

| ||

--- Enter main() --- This test may take several minutes to finish USXGMII setup at 1000Mbps ChanId 1, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x0 ChanId 1 Single frame interrupt example passed ChanId 2, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x10 ChanId 2 Single frame interrupt example passed ChanId 3, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x20 ChanId 3 Single frame interrupt example passed ChanId 4, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x30 ChanId 4 Single frame interrupt example passed ChanId 5, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x40 ChanId 5 Single frame interrupt example passed ChanId 6, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x50 ChanId 6 Single frame interrupt example passed ChanId 7, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x60 ChanId 7 Single frame interrupt example passed ChanId 8, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x70 ChanId 8 Single frame interrupt example passed ChanId 9, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x80 ChanId 9 Single frame interrupt example passed ChanId 10, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0x90 ChanId 10 Single frame interrupt example passed ChanId 11, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xA0 ChanId 11 Single frame interrupt example passed ChanId 12, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xB0 ChanId 12 Single frame interrupt example passed ChanId 13, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xC0 ChanId 13 Single frame interrupt example passed ChanId 14, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xD0 ChanId 14 Single frame interrupt example passed ChanId 15, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xE0 ChanId 15 Single frame interrupt example passed ChanId 16, Dest MacAddr: 0x0 0x0 0x53 0xE 0x9F 0xF0 ChanId 16 Single frame interrupt example passed Test passed --- Exiting main() --- |

Change Log

2021.2

https://github.com/Xilinx/embeddedsw/blob/xlnx_rel_v2021.2/doc/ChangeLog#L72

2021.1

https://github.com/Xilinx/embeddedsw/blob/xlnx_rel_v2021.1/doc/ChangeLog#L323

Related Links